Hi Team,

I have one question about TXS0104E and need your quick support.

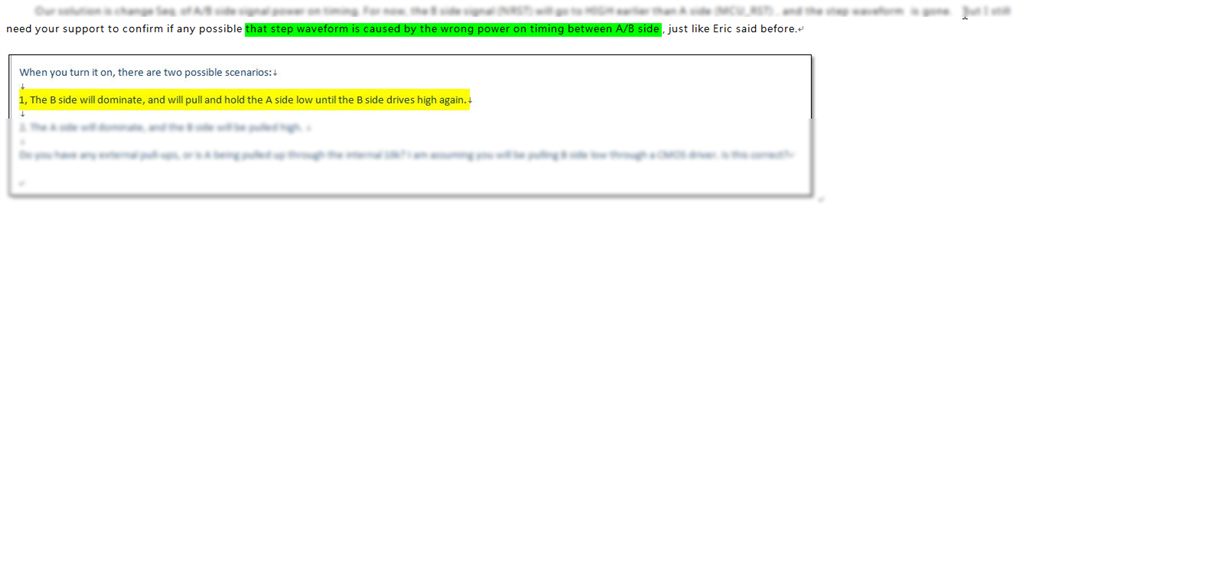

When TXS0104E A side signal has been PU to High, but B side signal still keep Low,and then TXS0104E is turned on, whether A signal will be shortly pull low (not to 0V) for a few (ms)time, then back to High again ?

Please refer to below waveform we measured , if unmount TXS0104E , then won’t see the NRST step rising delay. Please help to give me some comments, thank you.