Hi Team,

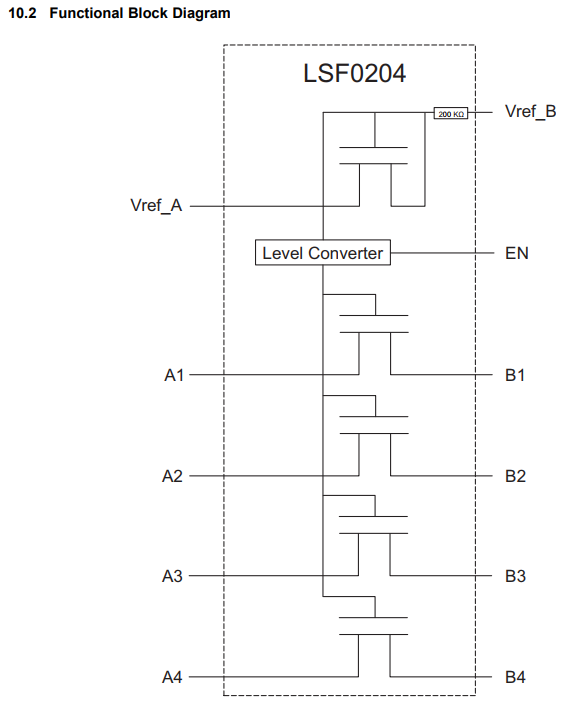

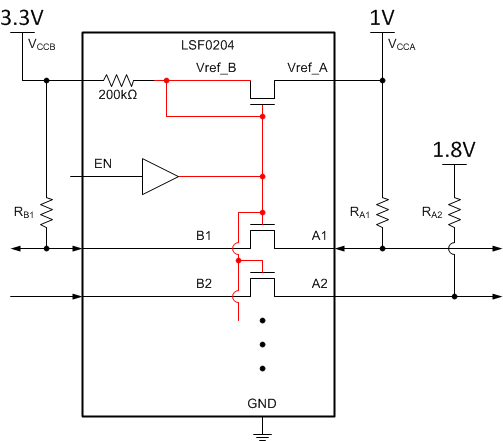

After reading LSF0204 datasheet and app notes,

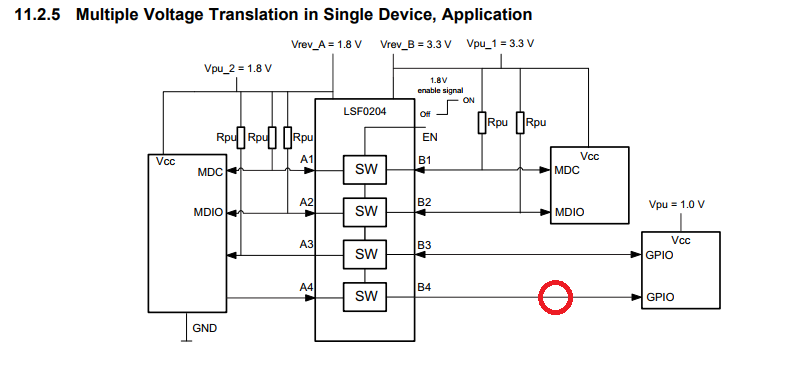

Where customer and I both cannot understand is why the red mark below don't need a pull up resistor?

Because the Vcc 1V is much small than Vref_B voltage. I cannot understand how this would work (I mean what voltage will appear at B4 pin?), please kindly teach me, thanks.

Andrew