Hello,

We have a FAN controller on side 1 and a FAN on side 2. We are experience an issue that “when Side B FAN is not connected the are experience clamping on side 1 to ~1 to 1.2V”. In other words, side A is limited to 0V and 1.2V levels. The pullup resistor for SDA2 is built into the fan so my suspicion is that the side 2 is settling to a voltage below the side 2 low threshold and that a low is being passed to side 1 when the fan is disconnected. However, if this were the case then side 1 should be “clamping” at 650mV to 800mV.

Looking at the specs of an analogous pin-to-pin part from another vendor, there spec implies that Side 1 voltage is limited to less than what side 2 voltage is. Is this true for a TI device. In other words, If SDA2 is sitting at 2V, would SDA1 be limited to 2V as well? I doubt this is the case, but please confirm.

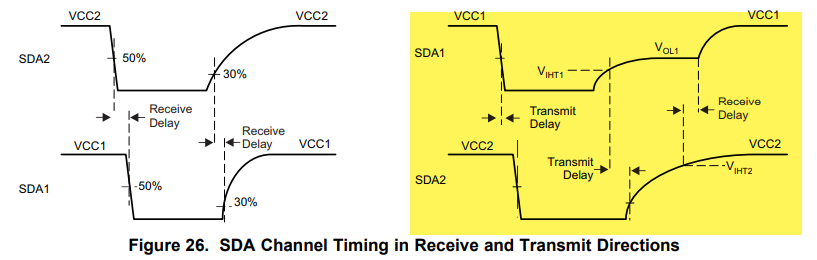

Also, what may help me further debug this is a easier to understand explanation of Figure 26 in the ISO1540 datasheet. Specifically the right-side image (also pasted below). I’m confused as to what is causing Vol1 in the image. Please elaborate.

Thank you