Hello, all

Now we have one inquiry regarding suitable D-Type Flip-Flop solution for clock dividing from our customer.

Please refer to the item below, and feedback us with your comment.

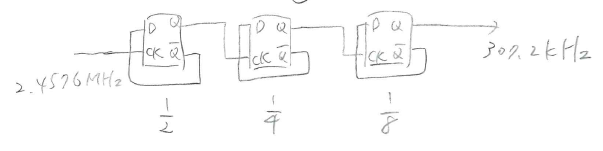

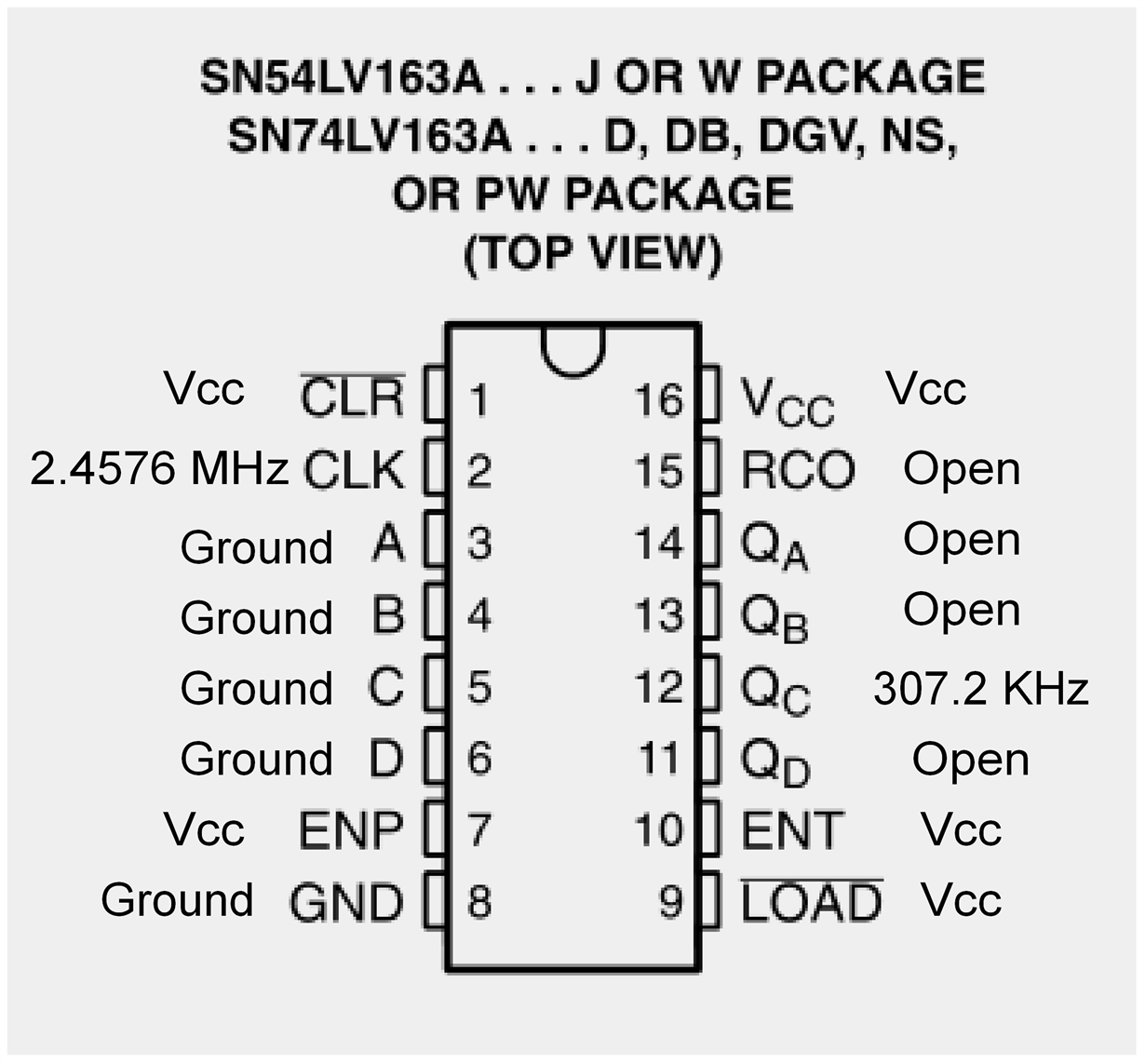

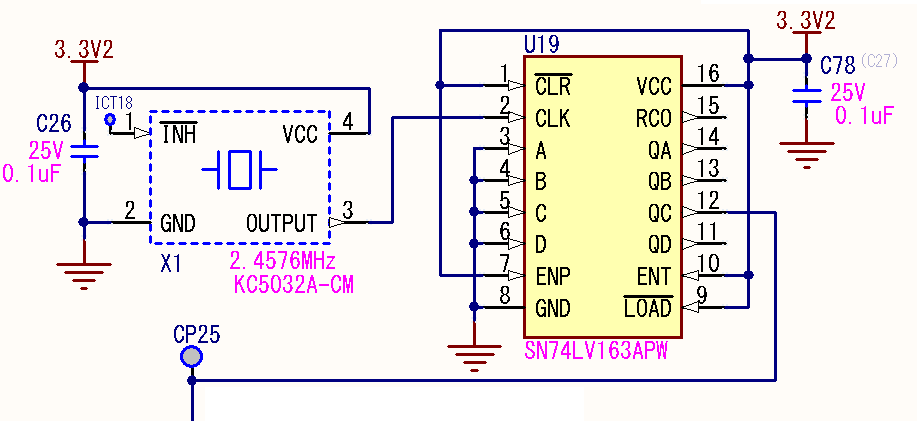

We are trying to design clock dividing circuit from 2.4576MHz to 307.2kHz (3.3V).

On this case, we assume that D-Type Flip-Flop could simply be used as following device configuration.

Based on this, please let us know which D-Type Flip-Flop solution would be most suitable.

We thank you in advance for your information.

Best regards,