Dear,

I'm using 74ALVC244Pw as output buffer for synchronisation signal 25Hz and 25kHz.

Line are used 2 by 2, delay between these 2 signal must be reduce, so I have chosen a fast logic.

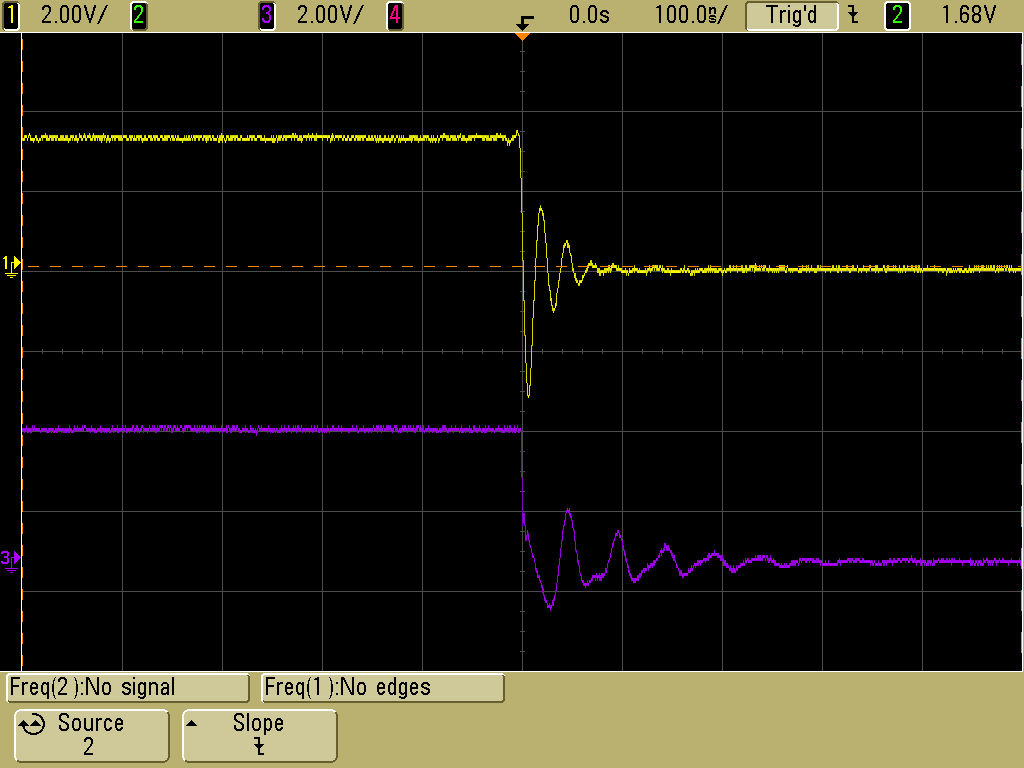

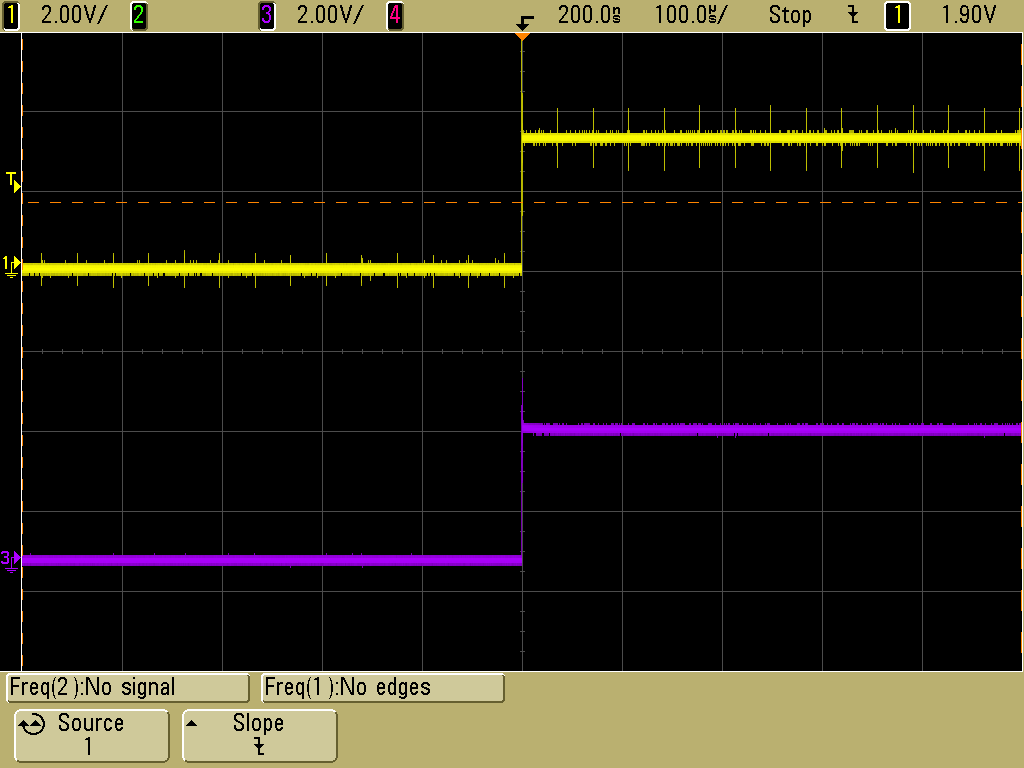

74ALVC244PW is OK for speed, but there are overshoot on the output. Overshoot level is 70% : 5V for a 3.3 TTL logic. Ouput capacitor is 100pf for ESD.

How can I reduce overshoot with modifications as low as possible. I may increase output capacitor ?

Regards,

Aymeric