Hi all,

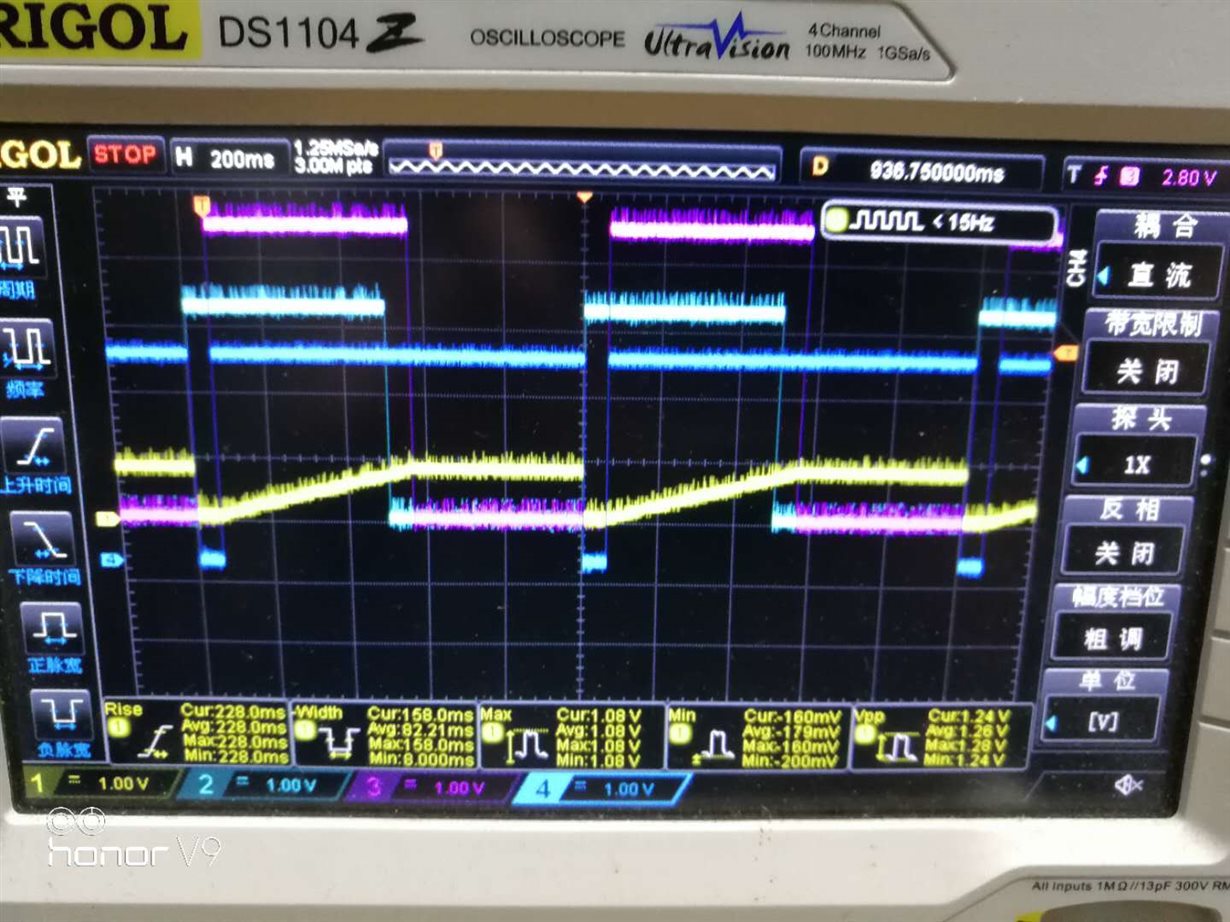

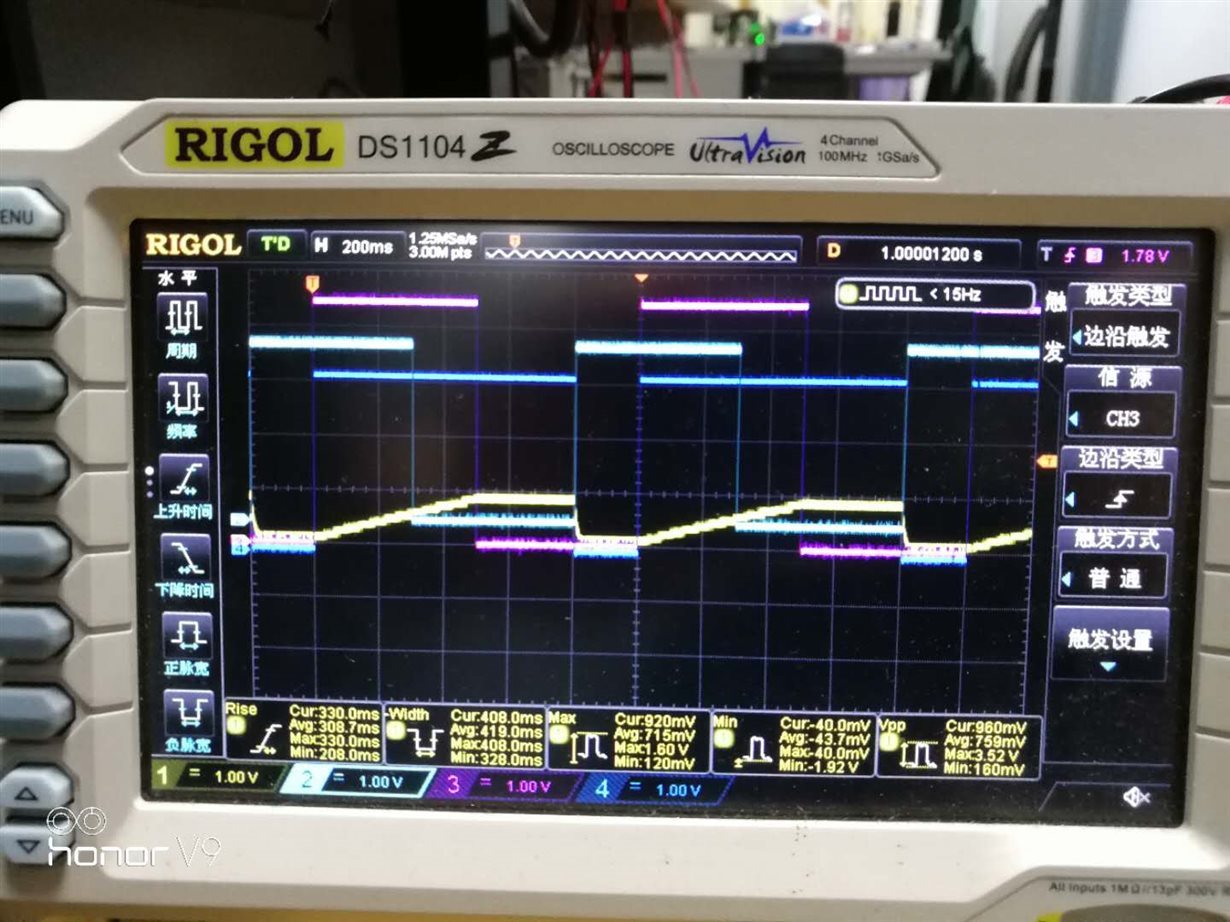

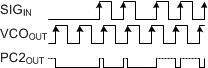

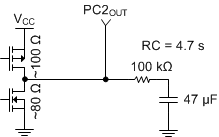

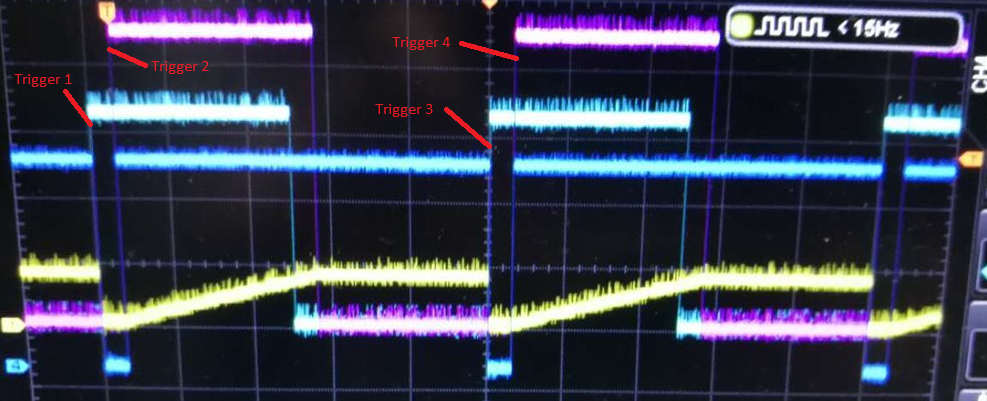

One customer use CD74HC4046 to make phase discrimination for two signals (1 hz). He wants to take advantage of the signal PC2out after filter as VCXO control signal. When PC2out disconnect to any devices, the phase discrimination signal can be seen obviously. But when a RC low-pass filter connected after PC2out, the phase discrimination signal will disappear, the filter output is close to zero.

In normal condition, the DC voltage after the filter should be close to 1V, but it is not clear why he lost the phase discrimination output signal after connecting with RC filter. The RC filter parameter is R=10k, C=10uF, because the input is 1Hz signal, so the RC bandwidth is very low.

Could you explain the root reason that may cause this issue and tell the method to solve it?

Thank you.