Other Parts Discussed in Thread: SN74LVC1G17

Hello!

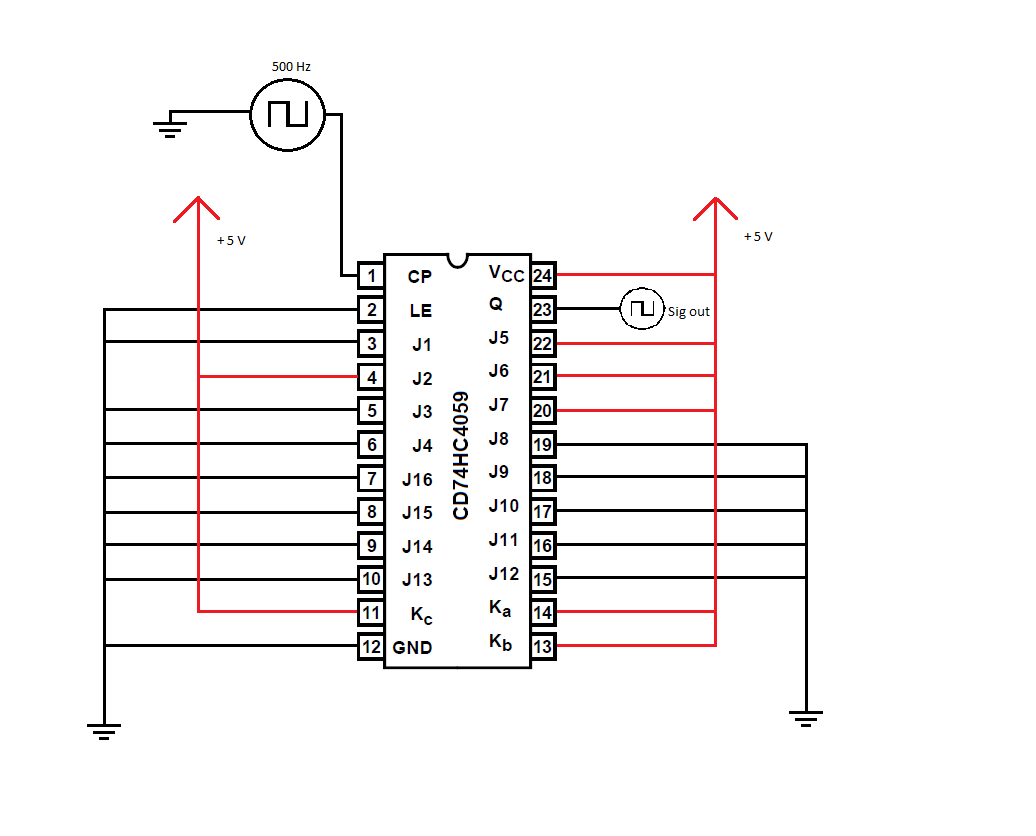

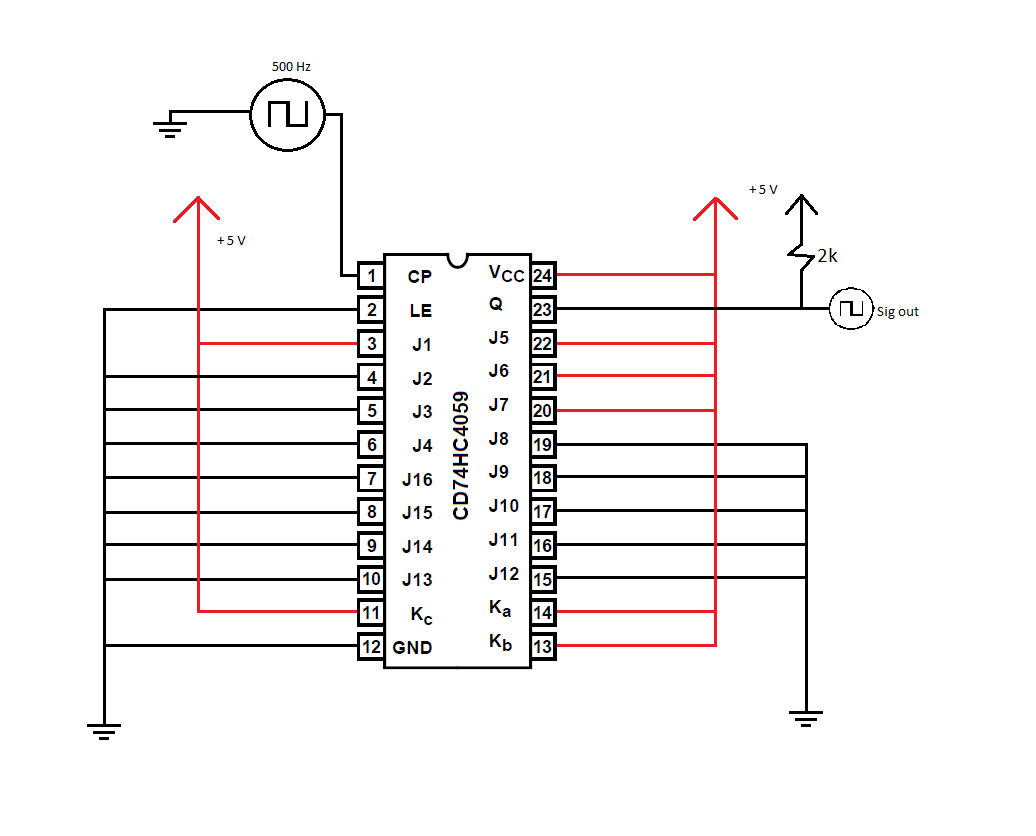

I've developed a frequency divider using the said part number based on the help of a previous thread. Though, we only discussed the J and K pins on that thread, and nothing else.

Notes:

- I am basing the configuration on the assumption that "high" refers to Vcc, and "low" refers to GND

- I currently have the device set for mode 2

- N=15, Vcc = 5V, freq_in = 500 Hz (connected to pin 1, CP) square wave

- The J and K pins are connected directly to Vcc or GND depending on the pin (no resistors are being used)

- Latch Enable (LE pin 2) is connected directly to GND

- This circuit is created on a breadboard and I am using a SOIC to DIP adapter

My Issue:

- I am not receiving any output signal with LE connected to GND

- If I connect LE to Vcc, I receive an attenuated version of the input signal (same frequency, less voltage)

- If I leave LE floating, I do not receive any output signal

Please help! I am not entirely sure what to do with the LE pin.

Thanks in advance,

Gage