Hello,

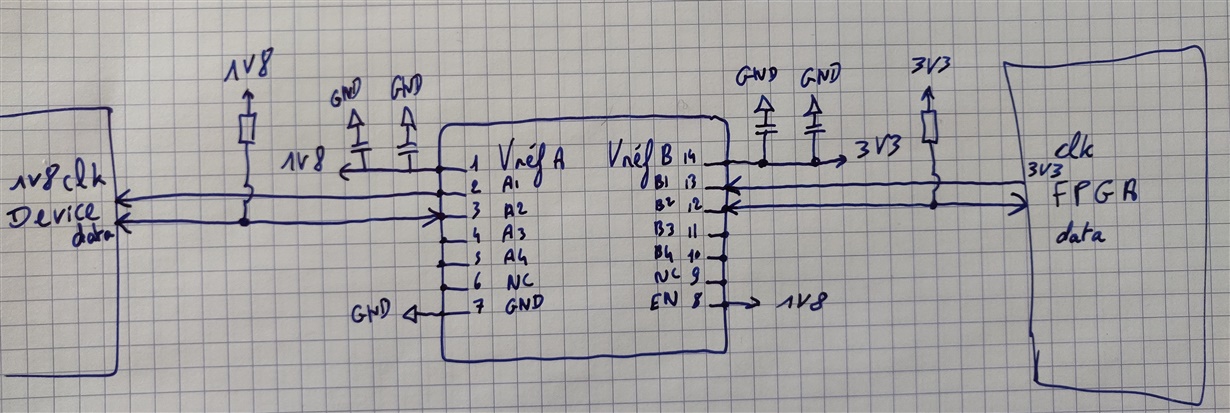

I am using a LSF0204 with two signals, one clock and one data.

I am doing a down translation for the clock and a bidirectional translation for the data.

i translate between 3.3v and 1.8v @ 1MHz.

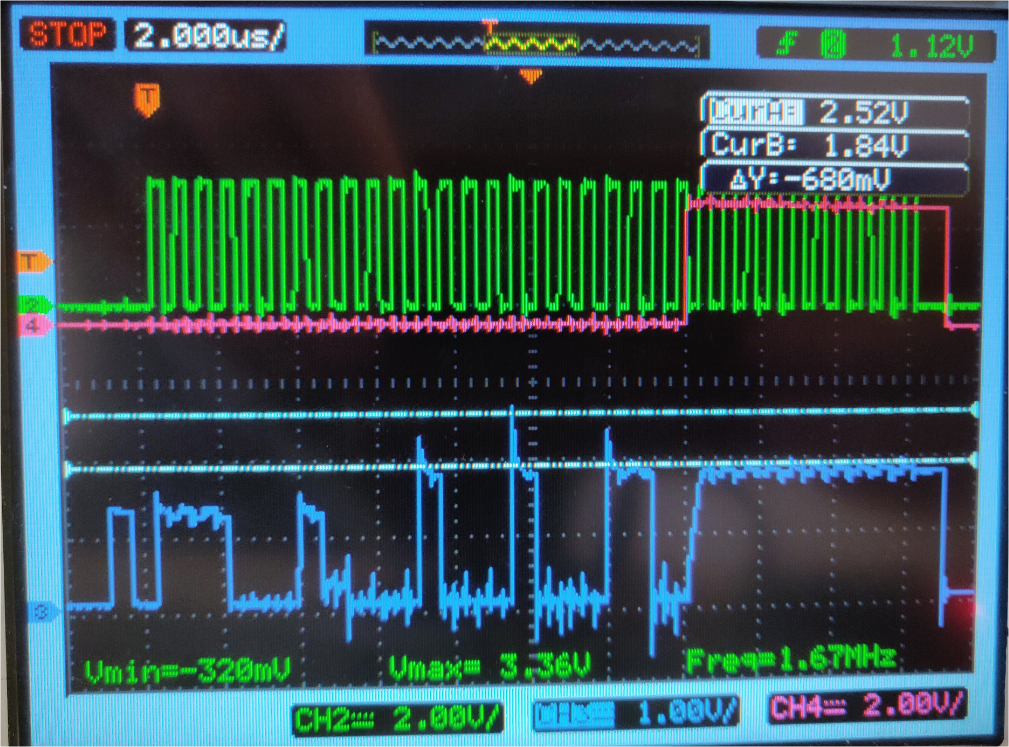

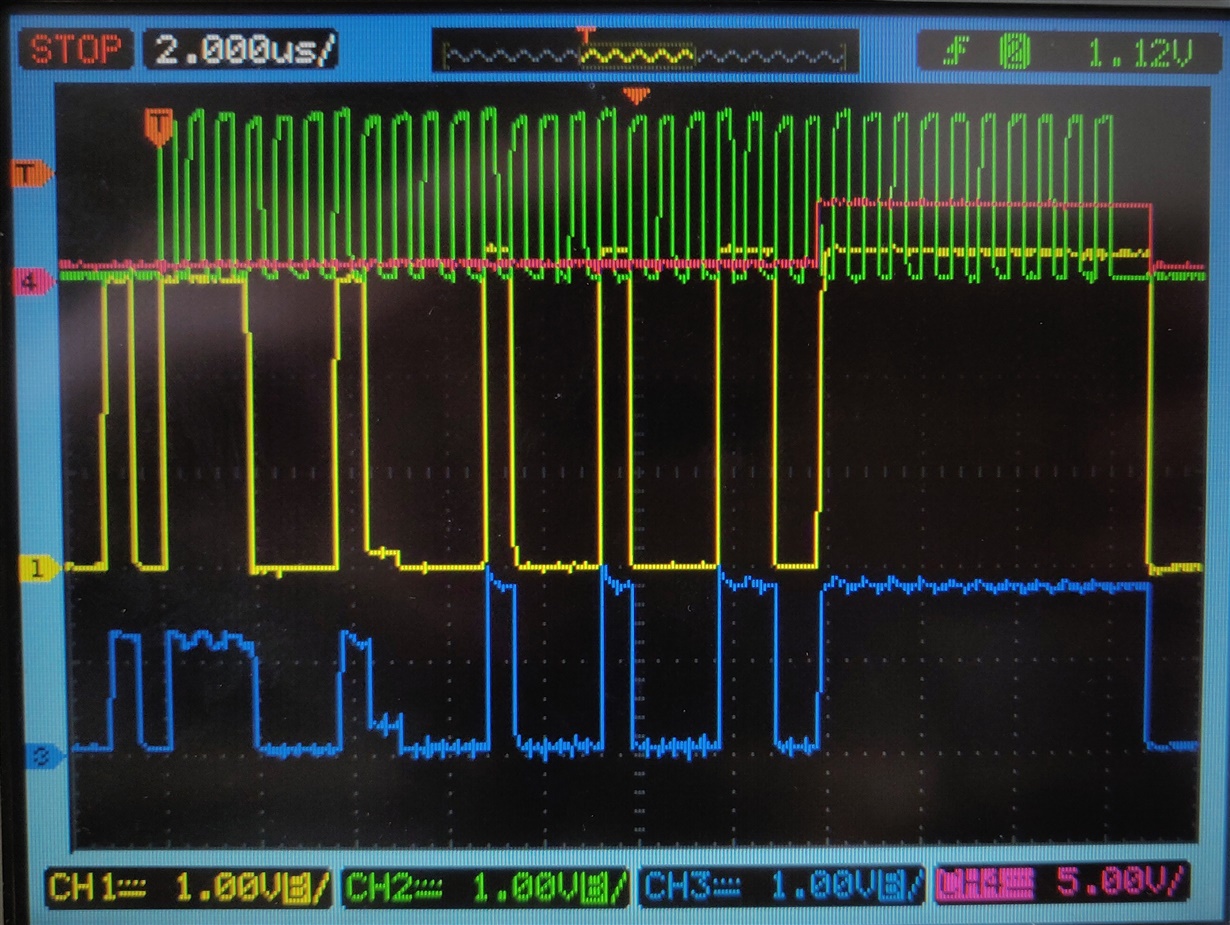

Here is a scope capture (sorry for the poor ground connection...) but my problem is that the data in blue is something like clamped at the beginning of the frame.

Except the beginning, the translation is well done.

I have pull-up resistor on each side of LSF on data line.

I tried different values without improvement.

BR