Hi Sir,

Please help me clarify, Thanks

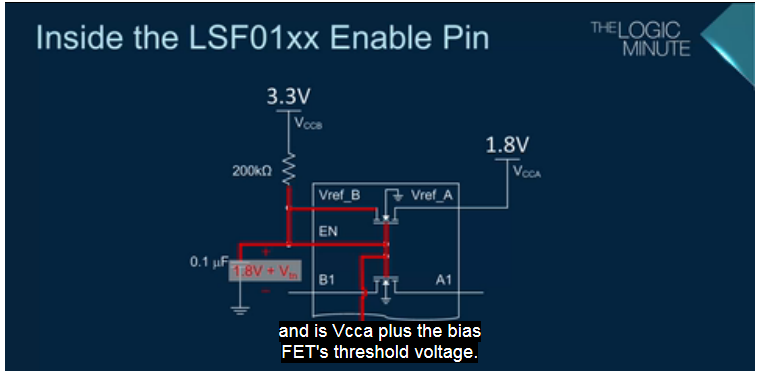

1. As the pic shown as below, Vref_B is determined by Vref_A + Vth. LSF01 seems have power sequence right? Vref_A should power up before Verf_B right?

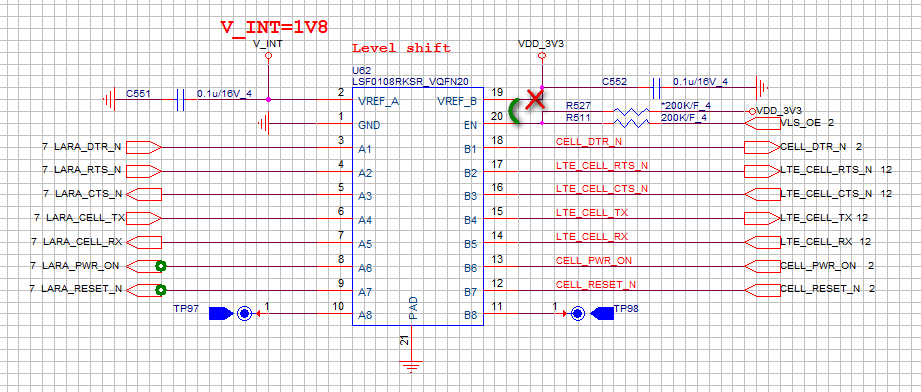

2. I did some rework, power up Vref_A 1.8V first and I can get 2.6V on Verf_B. Port B signal level still are 3.2V. But why port A signal is 2.0V not 1.8V? should we add pull-up resistor to 1.8V on port_A?

3. In our currently design, VDD_3V3(actually 3.2V) power up before V_INT, I think that’s why we can get 2.4V on Vref_A, correct?