I am running a 28069 and I am having a strange problem with the eCap function.

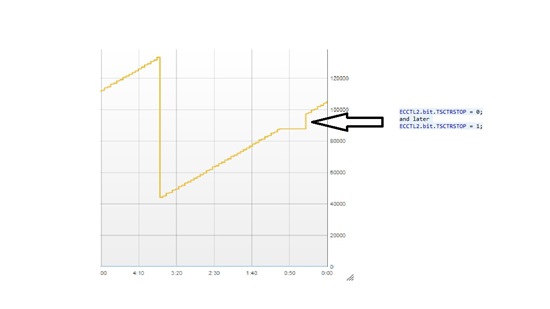

I have traced the problem to being related to the TSCTR value jumping up and down.

When I read out the TSCTR value in each program run, then the read value goes both up and down.

I have tried to reset the TSCTR using the SWsync, however I can not get the TSCTR to reset to 0.

I have also noticed that when I stop the TSCTR, then when I start it again, then the value read from TSCTR jumps to a much higher value.

This however does not comply with the description in "spruh18e.pdf"

Attached is a picture of the TSCTR value being read from the uP.

Any suggestions to what I am doing wrong?

Register setup:

DINT; //disable global interrupts

pEcapRegs->ECCTL2.bit.TSCTRSTOP = 0; // Stop the counter

pEcapRegs->ECEINT.bit.CEVT1 = 0; //disable all eCAP interrupts

pEcapRegs->ECEINT.bit.CEVT2 = 0;

pEcapRegs->ECEINT.bit.CEVT3 = 0;

pEcapRegs->ECEINT.bit.CEVT4 = 0;

pEcapRegs->ECEINT.bit.CTROVF = 0;

pEcapRegs->ECEINT.bit.CTR_EQ_CMP = 0;

pEcapRegs->ECEINT.bit.CTR_EQ_PRD = 0;

pEcapRegs->ECCTL1.bit.CAP1POL = EC_RISING; // Capture Event 1 Polarity select (EC_RISING, EC_FALLING)

pEcapRegs->ECCTL1.bit.CTRRST1 = EC_ABS_MODE; // Counter Reset on Capture Event 1 (EC_ABS_MODE, EC_DELTA_MODE)

pEcapRegs->ECCTL1.bit.CAP2POL = EC_FALLING;

pEcapRegs->ECCTL1.bit.CTRRST2 = EC_DELTA_MODE;

pEcapRegs->ECCTL1.bit.CAPLDEN = 1; // Enable Loading CAP1-4 regs on a Cap Event

pEcapRegs->ECCTL1.bit.PRESCALE = EC_DIV1; // Event Filter prescale select

pEcapRegs->ECCTL1.bit.FREE_SOFT = 3; // Emulation mode - 11 = ignore emulation suspend

pEcapRegs->CTRPHS = 0;

pEcapRegs->ECCTL2.bit.CONT_ONESHT = EC_CONTINUOUS; // EC_CONTINUOUS, EC_ONESHOT

pEcapRegs->ECCTL2.bit.STOP_WRAP = EC_EVENT2; // "Stop value for one-shot, Wrap for continuous"

pEcapRegs->ECCTL2.bit.REARM = 1; // One-shot re-arm (0, EC_ARM)

pEcapRegs->ECCTL2.bit.SYNCI_EN = 1; // Counter sync-in select, 0 = disable Sync-In

pEcapRegs->ECCTL2.bit.SYNCO_SEL = EC_SYNCO_DIS; // Sync-out mode (EC_SYNCIN, EC_CTR_PRD, EC_SYNCO_DIS)

pEcapRegs->ECCTL2.bit.SWSYNC = 1; // SW forced counter sync, 0 = no action (no s/w synch)

pEcapRegs->ECCTL2.bit.CAP_APWM = EC_CAP_MODE; // CAP/APWM operating mode select (EC_CAP_MODE, EC_APWM_MODE)

pEcapRegs->ECCTL2.bit.APWMPOL = EC_ACTV_HI; // APWM output polarity select (EC_ACTV_HI, EC_ACTV_LO)

pEcapRegs->ECCLR.all = 0x00ff;

pEcapRegs->ECCTL2.bit.TSCTRSTOP = EC_RUN; // TSCNT counter stop (EC_FREEZE, EC_RUN)

EINT;