Hi,

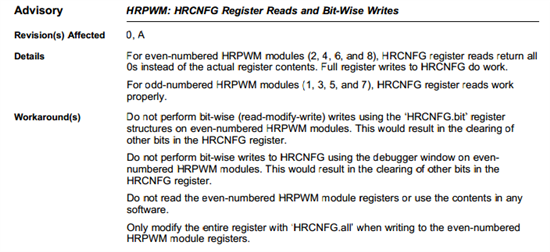

I have a problem setting up the HRPWM registers of my F28377D controller: I am using the routine prescribed on TI's wiki (see below) but the weirdest thing happens. If I step by step go through the for loop for successively initializing the HRPWM of my ePWM1, ePWM2,... ePWM10 modules then I can ONLY WRITE TO ODD ePWM modules: ePWM1.HRCFNG register will be set properly when ePWM2, ePWM4, ePMW6 will not!

I also tried to set ePWM3.HRCFNG directly and that didn't work either.

I am really puzzled...Is that a bug ?

Thanks in advance for your help,

Regards,

Francois.

Uint16 j;

// ePWM channel register configuration with HRPWM

// ePWMxA / ePWMxB toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

for (j=1;j<=NB_IMPEDANCE_BURST_CHANNELS;j++)

{

(*eHRPWM[j]).TBCTL.bit.PRDLD = TB_IMMEDIATE; // set Immediate load

(*eHRPWM[j]).TBPRD = PWM_5MHZ_MODULATION_PERIOD-1; // PWM frequency = 1 / period

(*eHRPWM[j]).CMPA.half.CMPA = PWM_5MHZ_MODULATION_PERIOD / 2; // set duty 50% initially

(*eHRPWM[j]).CMPA.half.CMPAHR = (1 << 8); // initialize HRPWM extension

(*eHRPWM[j]).CMPB.half.CMPB = PWM_5MHZ_MODULATION_PERIOD / 2; // set duty 50% initially

(*eHRPWM[j]).CMPB.all |= (0 << 8); // initialize HRPWM extension

(*eHRPWM[j]).TBPHS.all = 0;

(*eHRPWM[j]).TBCTR = 0;

(*eHRPWM[j]).TBCTL.bit.CTRMODE = TB_COUNT_UP;

(*eHRPWM[j]).TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;

(*eHRPWM[j]).TBCTL.bit.HSPCLKDIV = TB_DIV1; // ePWM CLK = SYSCLOCK

(*eHRPWM[j]).TBCTL.bit.CLKDIV = TB_DIV1;

(*eHRPWM[j]).TBCTL.bit.FREE_SOFT = 11;

(*eHRPWM[j]).CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

(*eHRPWM[j]).CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

(*eHRPWM[j]).CMPCTL.bit.SHDWAMODE = CC_SHADOW;

(*eHRPWM[j]).CMPCTL.bit.SHDWBMODE = CC_SHADOW;

(*eHRPWM[j]).AQCTLA.bit.ZRO = AQ_SET; // PWM toggle high/low

(*eHRPWM[j]).AQCTLA.bit.CAU = AQ_CLEAR;

(*eHRPWM[j]).AQCTLB.bit.ZRO = AQ_SET;

(*eHRPWM[j]).AQCTLB.bit.CAU = AQ_CLEAR;

EALLOW;

(*eHRPWM[j]).HRCNFG.all = 0x0;

(*eHRPWM[j]).HRCNFG.bit.EDGMODE = HR_FEP; // MEP control on falling edge

(*eHRPWM[j]).HRCNFG.bit.CTLMODE = HR_CMP;

(*eHRPWM[j]).HRCNFG.bit.HRLOAD = HR_CTR_ZERO;

(*eHRPWM[j]).HRCNFG.bit.EDGMODEB = HR_FEP; // MEP control on falling edge

(*eHRPWM[j]).HRCNFG.bit.CTLMODEB = HR_CMP;

(*eHRPWM[j]).HRCNFG.bit.HRLOADB = HR_CTR_ZERO;

(*eHRPWM[j]).HRCNFG.bit.AUTOCONV = 1;

(*eHRPWM[j]).HRPCTL.bit.HRPE = 0; // Turn 0 high-resolution period control.

(*eHRPWM[j]).TBCTL.bit.PHSEN = TB_DISABLE;

(*eHRPWM[j]).HRPCTL.bit.TBPHSHRLOADE = 0;

EDIS;

}