I started with the 2 HRPWM examples (hrpwm_duty_sfo and hrpwm_prdupdown_sfo) and I don't see what I expect.

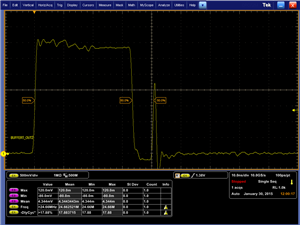

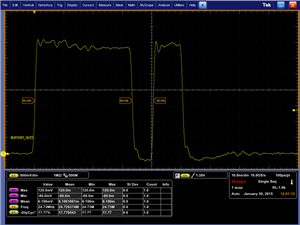

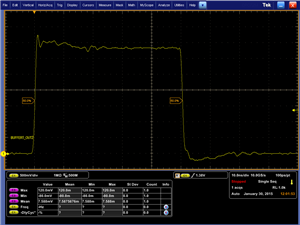

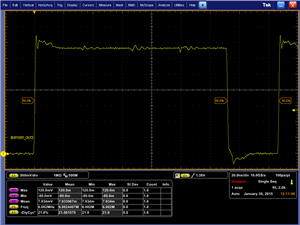

On the duty example, the MEP appears to function, but there is a range at the lower end of the duty-cycle that is produced that appears to have a cycle low and high in the middle of the pulse (obviously turning it into two shorter pulses). Strange.

For the prdupdown example there is a problem with the MEP behavior. It never moves the edge finer than the 60 MHz EPWM clock rate. One behavior that I don't understand is that the example holds the TBPRD fixed (meaning the EPWM edge should not be changing) and only the TBPRDHR register is modified, meaning I would expect only MEP sized changes in the period. What I observe is that the edge moves by 16.8 ns (one tick of a 60 MHz clock, which is what the EPWM should be running at if I read the example code correctly) over the entire sweep of TBPRDHR settings that are written by the example.

Are you able to reproduce any of this on your end? I assume these examples apply to other devices as well and perhaps have not actually been tried on this new chip.