Hi all,

I need to send 1024 16bit words via SPI as master to a slave with frame (word) synchronization. Therefore I decided to use the McBSP-A and one additional DMA channel to load the DXR1 register.

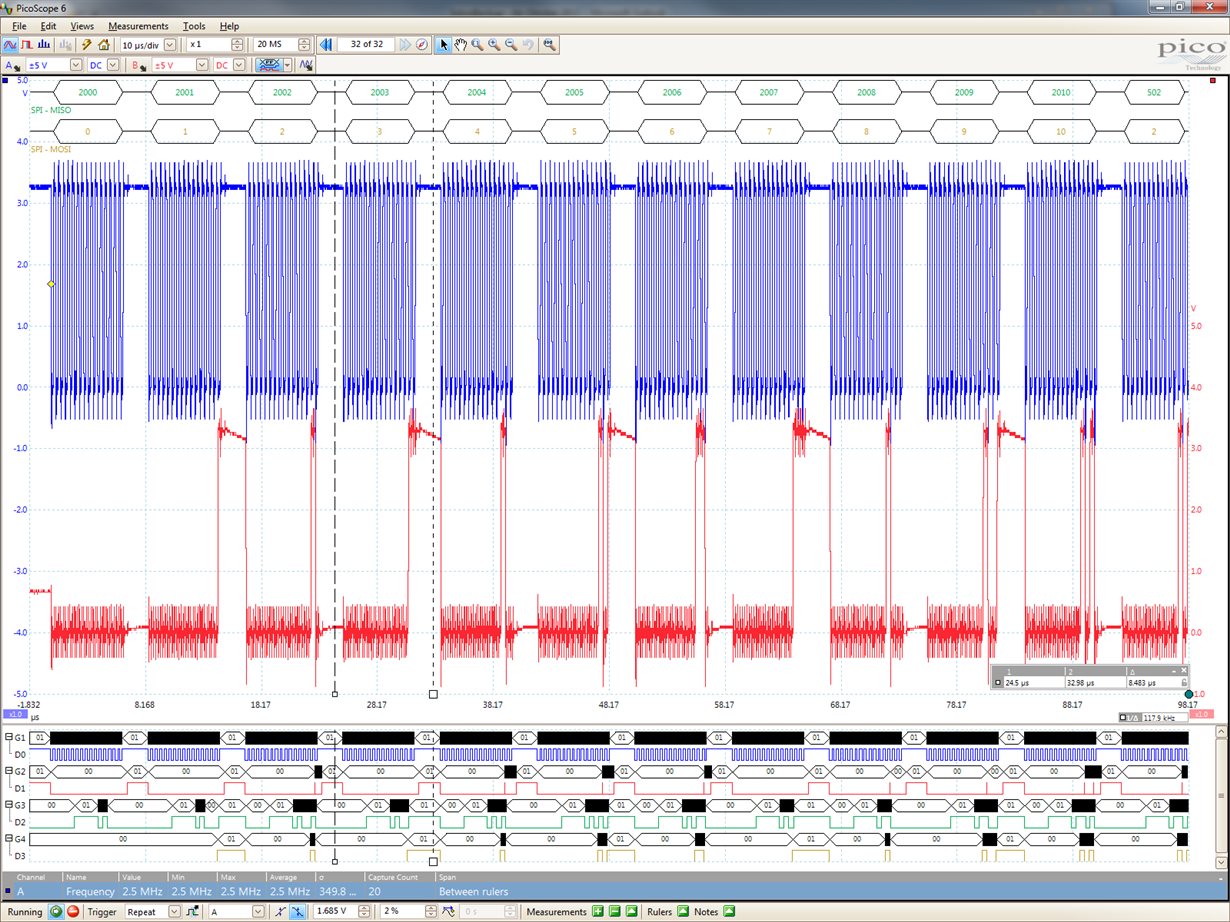

So far I have been successful but I always see pauses during frame sync phase (figure below)

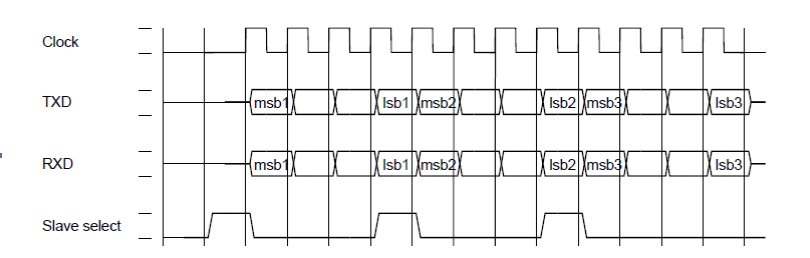

What I need is a solution without any pauses at the clock line and a frame sync signal parallel to the LSB of every word (figure below).

Does anybody know a solution with details regarding McBSP configuration. I tried to setup frames with one 16bit word and maximum frame frequency but haven’t been successful up to know.

Every suggestion is appreciated.

Regards

Andreas