Hi All,

I have a working program for this embedded system. It's been running in debug and release modes without issue, until adding a write-to-flash feature.

I write calibration variables to flash, so they will survive a power/reboot cycle.

The routines write to Sector E as expected. I can see that in debug mode.

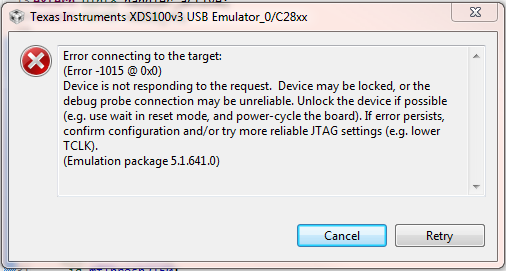

Here's the problem: When thecode is built in release mode, and uploaded to the device, everythings works fine, except the emulator will no longer connect to the target. Here's the error message:

After replacing the DSP chip, all is well again, until running the write to flash routine.

Here's the breakdown of the routine, it's called store_config(): (feel free to ignore the circles and arrows)

Running the "Test Connection" utility in CCS 6 returns no problems. It seems like the CSM password has been written to, and so it locks out the emulator connection. But I can't find any reason for that memory to be written to.

Any ideas would be greatly appreciated.

Thanks for your input!