Hello Sir,

I am Sandip Rakhasiya. Currently I am using F28M35H52C1 controller.

In which I have used SPI at DSP C28 side. I have used 15 MBPS Bitrate for SPI. Here I have to total transmit/receive 64 data in only 100 microsecond but it nearer to 125 micro second. But Here We have only 16 Fifo so i can not transmit more than 16 words at one time. So I have to transmit 16 words x 4 times.

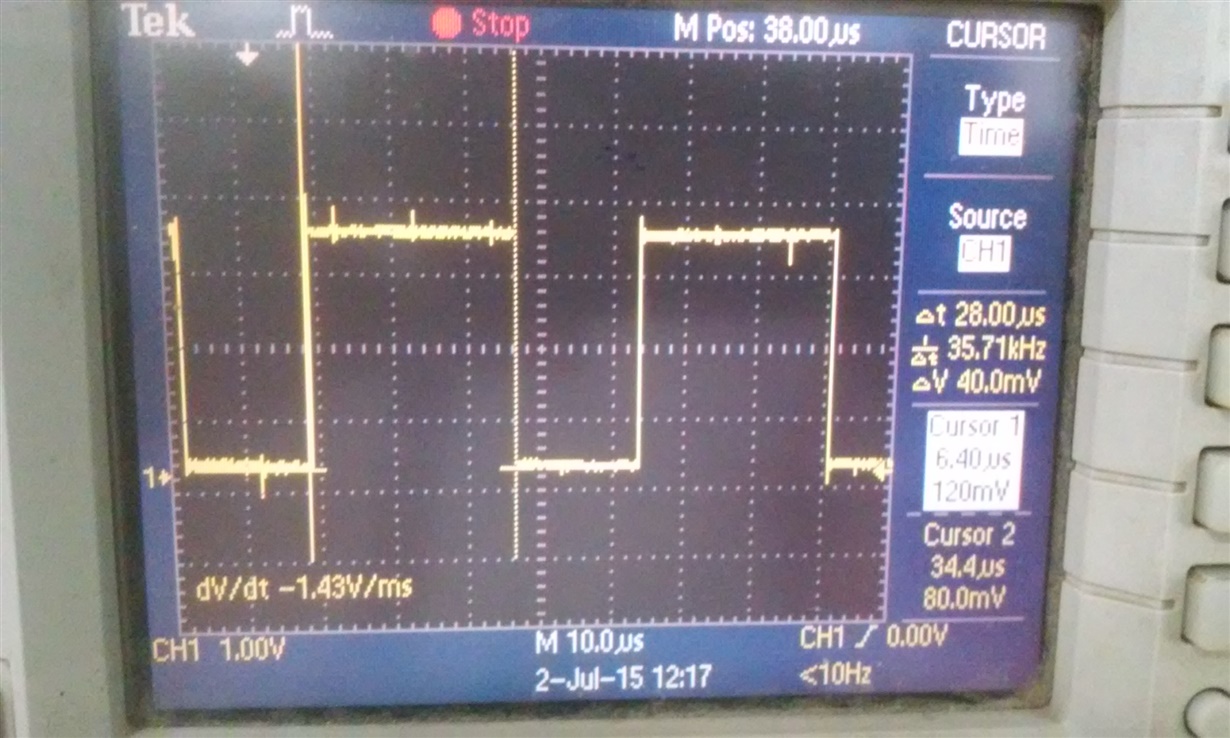

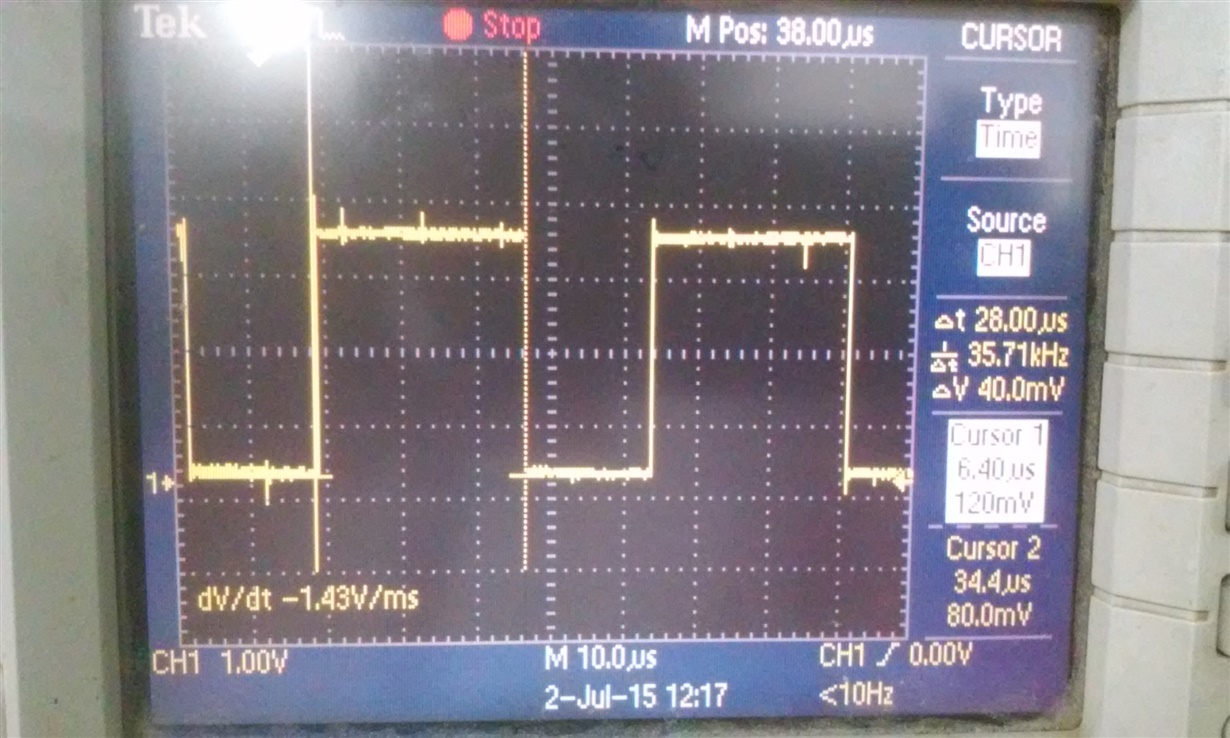

Now When i am transmitting, there is some gap between regular transmit. I have few picture of CS line. In this CS line, 17-18 microsecond required for transmit and after that 25-28 microsecond, it goes to high and after that new 16 words transmited.

In this way I am not understanding, why CS stayed at high for 25-28 microsecond. Is there any solution to remove this gap ?