Hi ,

I am trying to run complimentary pair PWM's for my dc motor. I turn on and turn off the PWM's in intervals .

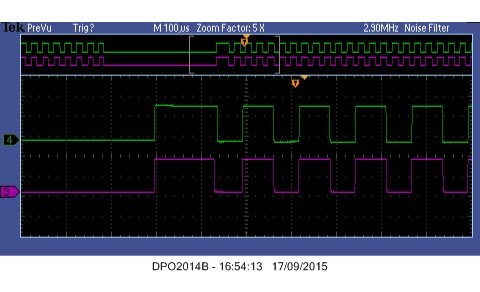

When I turn ON my PWM's , the first cycle always seems to have a longer duty cycle compared to the rest of the PWM cycles .

Could you please tell me why this happens.

Kind Regards

Anish