Hi all,

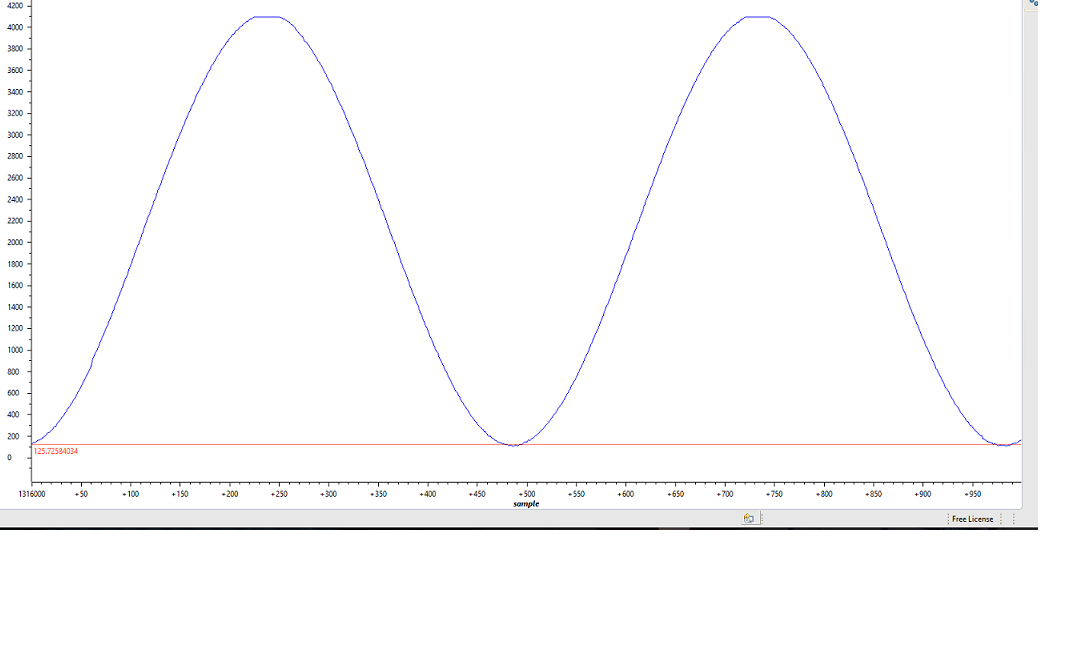

Please I will be glad if anyone can help me trace this problem. I am sampling a 50 Hz Input sinusoidal signal using ADC of TMS320F28379D (Experimenter Kit) and the sampling Frequency is 50kHz. When I graphed the AdcResult, I was expecting to get 1000 samples per period, but I am getting 500 samples per period. Below is the graph from CCS. Also below is the ADC and epwm settings: Thanks in advance for your help.

Note: EALLOW and EDIS were put where necessary.

AdcaRegs.ADCCTL2.bit.PRESCALE = 14; // Set ADCCLK divider to /8 i.e 25MHZ

AdcaRegs.ADCCTL2.bit.RESOLUTION = 0; // 12-bit resolution

AdcaRegs.ADCCTL2.bit.SIGNALMODE = 0; // Single-ended channel conversions (12-bit mode only)

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1; // Set pulse positions to late

AdcaRegs.ADCCTL1.bit.ADCPWDNZ = 1; // Power up the ADC

DELAY_US(1000);// Delay for 1ms to allow ADC time to power up

AdcaRegs.ADCSOC0CTL.bit.CHSEL = 3; // SOC0 will convert pin A3

AdcaRegs.ADCSOC0CTL.bit.ACQPS = 14; // Sample window is 75ns

AdcaRegs.ADCSOC0CTL.bit.TRIGSEL = 5; // Trigger on ePWM1 SOCA

AdcaRegs.ADCINTSEL1N2.bit.INT1SEL = 0; // End of SOC0 will set INT1 flag

AdcaRegs.ADCINTSEL1N2.bit.INT1E = 1; // Enable INT1 flag

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; // Make sure INT1 flag is cleared

//settings for epwm

EPwm1Regs.TBCTL.bit.CTRMODE = 0; // Count up

EPwm1Regs.TBPRD = 2000; // Set timer period for 50 kHz

EPwm1Regs.CMPA.bit.CMPA = EPwm1Regs.TBPRD / 2; // 50% duty cycle ;

EPwm1Regs.TBCTL.bit.PHSEN = 0; // Disable phase loading

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0; // HSPCLKDIV = 1

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1