Board: TMS320F2808

I have follow all the instruction manual of software & hardware to configure ADC module with external signal circuit.

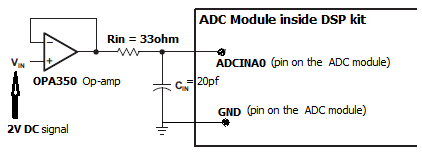

For stable & low impedance signal, i used OPA350 opamp, Resister Rin=33ohm, Capacitor Cin=20PF as per the reference guide "Analog Interface With 28xx

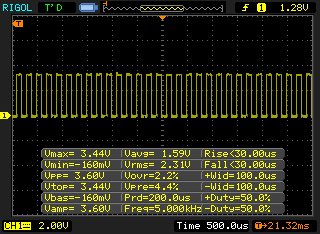

DSCs SPRAAP6.PDF". Then fed this stable & low impedance signal across ADC module of [ADCINA0 & GND] pins and starting the operation of Debugging & Run. But in [ADCRESULT0] register bit printing/calculating random digital value, which is not equivalent to analog input value.

What should i do to generate appropriate digital value?

Am i missing any steps to configure ADC?

Here i'm inserting hardware configuration:

Here i'm including software configuration:

void init_adc(void)

{

AdcRegs.ADCTRL3.bit.ADCCLKPS = 2; // ADC Clock Pre scaler (i.e 12.5MHz)

AdcRegs.ADCTRL3.bit.SMODE_SEL = 0; // Sequential model

AdcRegs.ADCMAXCONV.all = 0; // 1 Conv's on SEQ

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0; // Setup ADCINA0 as 1st SEQ Conv.

AdcRegs.ADCTRL1.bit.SEQ_CASC = 1; // Cascaded Sequencer Mode

AdcRegs.ADCTRL1.bit.SEQ_OVRD = 0; // disable SEQ overriding mode

AdcRegs.ADCTRL1.bit.CONT_RUN = 1; // Continuous Run mode

AdcRegs.ADCTRL1.bit.CPS = 0; // divide by 1

AdcRegs.ADCTRL1.bit.ACQ_PS = 7; // S/H=(1+ACQ_PS)*(time of ADCCLK)

AdcRegs.ADCTRL1.bit.SUSMOD = 0; // Emulation suspend is ignored

AdcRegs.ADCTRL2.bit.RST_SEQ1 = 0; // No action

AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1; // SEQ1 start from ePWM_SOCA trigger

AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1; // Enable SEQ1 interrupt request to CPU

AdcRegs.ADCTRL2.bit.INT_MOD_SEQ1 = 0; // Interrupt after every end of sequence

}

__interrupt void adc_isr(void)

{

unsigned int t;

unsigned int V[200];

for(t=0;t<10;t++)

{

V[t] = AdcRegs.ADCRESULT0; // Stores Digital value

printf("Digital Voltage: V[t]= %u \n", V[t]);

}

AdcRegs.ADCST.bit.INT_SEQ1_CLR = 1; // Clear INT SEQ1 bit

AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 0; // Disable SEQ1 interrupt

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; // Acknowledge interrupt to PIE

return;

}