Other Parts Discussed in Thread: REF3030, OPA2227

C2000 Team,

I am running the ADC-A on F28377S Launchpad in 12-bit mode, triggered from ePWM at 50 kHz rate, and acquisition window of 100 ns (20 cycles @ 200 MHZ SYSCLK). I am using the CPU to take a single 50 point buffer of data. After buffering 50 points, the ADC interrupt is disabled in the ISR so I buffer no more points. Conversion is on ADCINA0 channel.

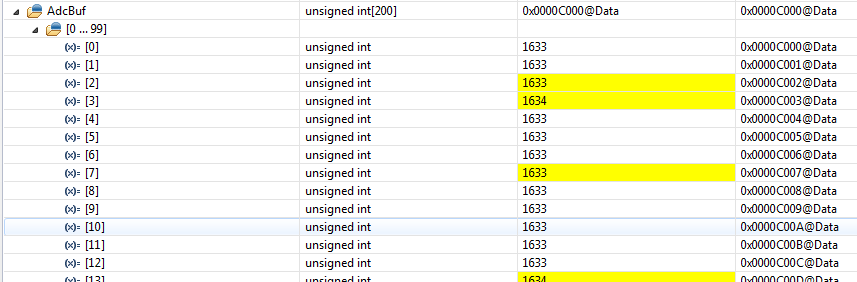

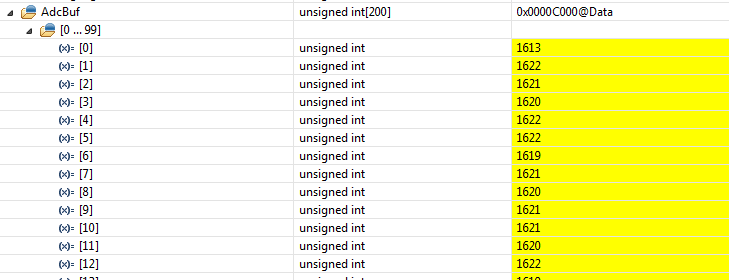

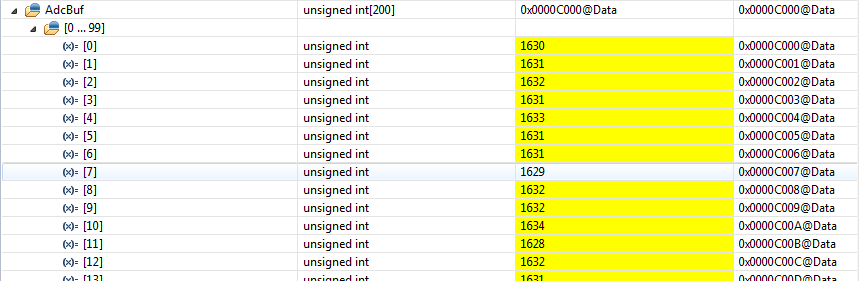

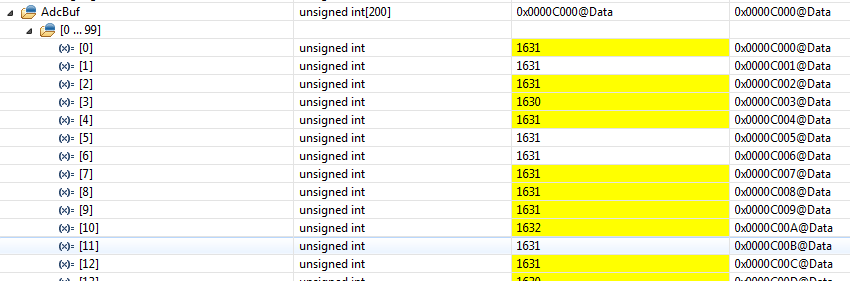

The problem is with the very first point. See graphs below. The input is a 1 kHz triangle wave running from about 0.2 to 3.1V. The very first point is always slightly off. You can see it in the CCS graphs below.

I added additional delay after enabling the ADCs before I trigger them with the ePWM. No difference.

I tried a different signal generator thinking maybe it was some sort of loading issue on the input. No difference.

I tried a different ADC (ADC-B). No difference.

I doubled the acquisition window to 200 ns. No difference.

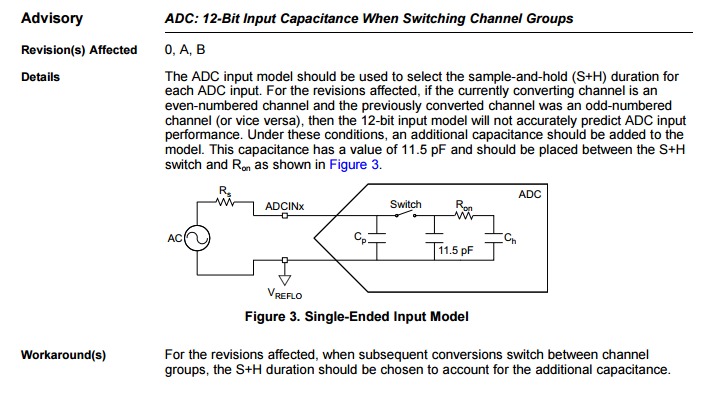

I checked the errata and don't see anything about a first sample error.

Now, I am using TMX silicon (rev.B), but this just doesn't seem like the problem. All the other samples are fine (with some apparent offset error).

Any ideas on what could be causing this?

Thanks and regards,

David