Hi ,

My customer uses C28346 .

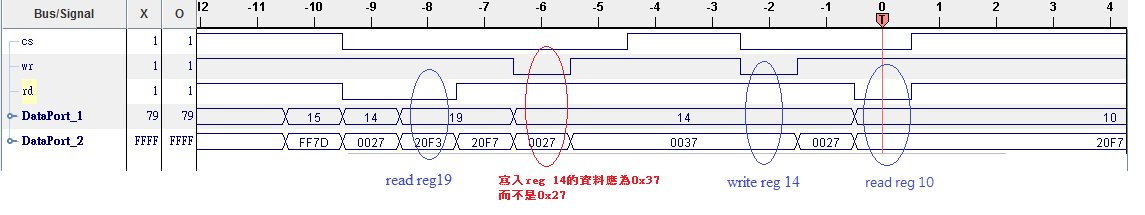

There is a issue with using EMIF to access CPLD.

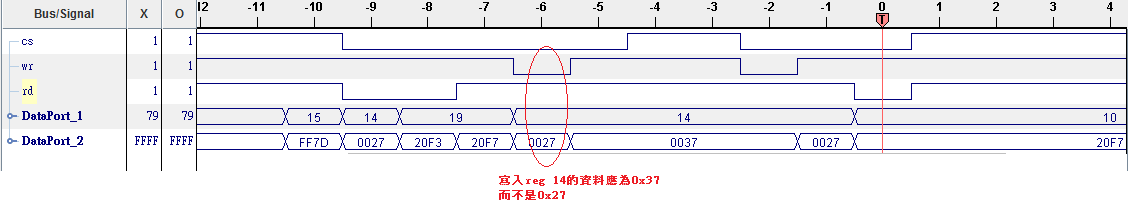

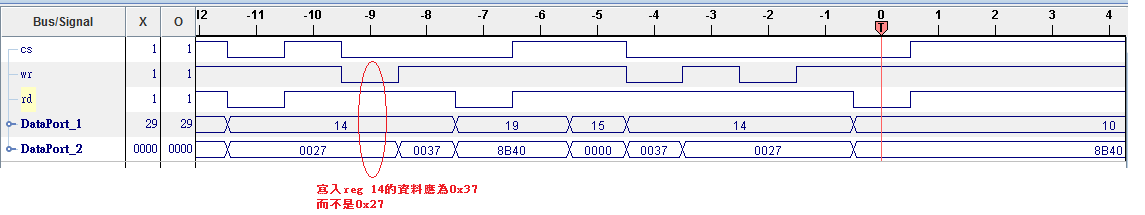

The problem is that the /WR signal is not synchronous with DATA BUS.

It expects that write a 0x37 to CPLD.

But in reality, it writes a old data 0x27 to CPLD .

After adding a "NOP" into fail code, the result is correct.

Question1: What is the reason causing that the /WR signal is not synchronous with DATA BUS ?

Question2: What the correct solution is?

thanks,

best regards,

Simen

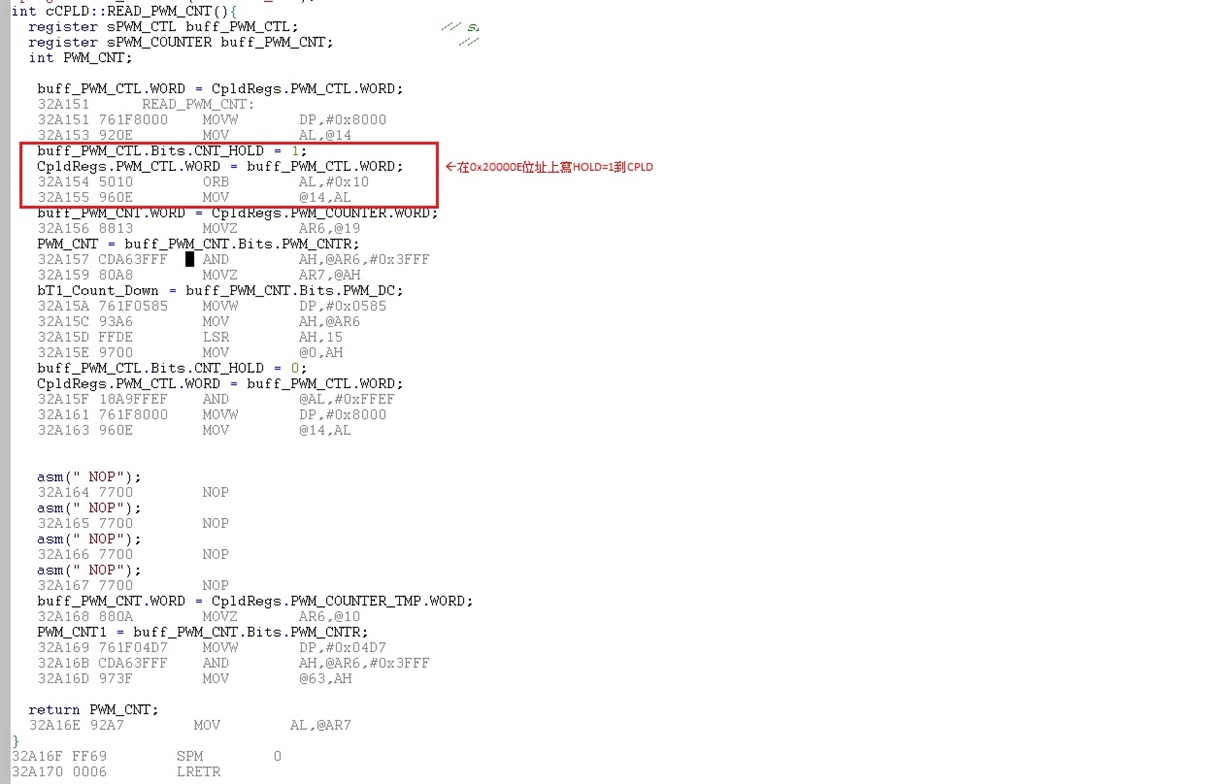

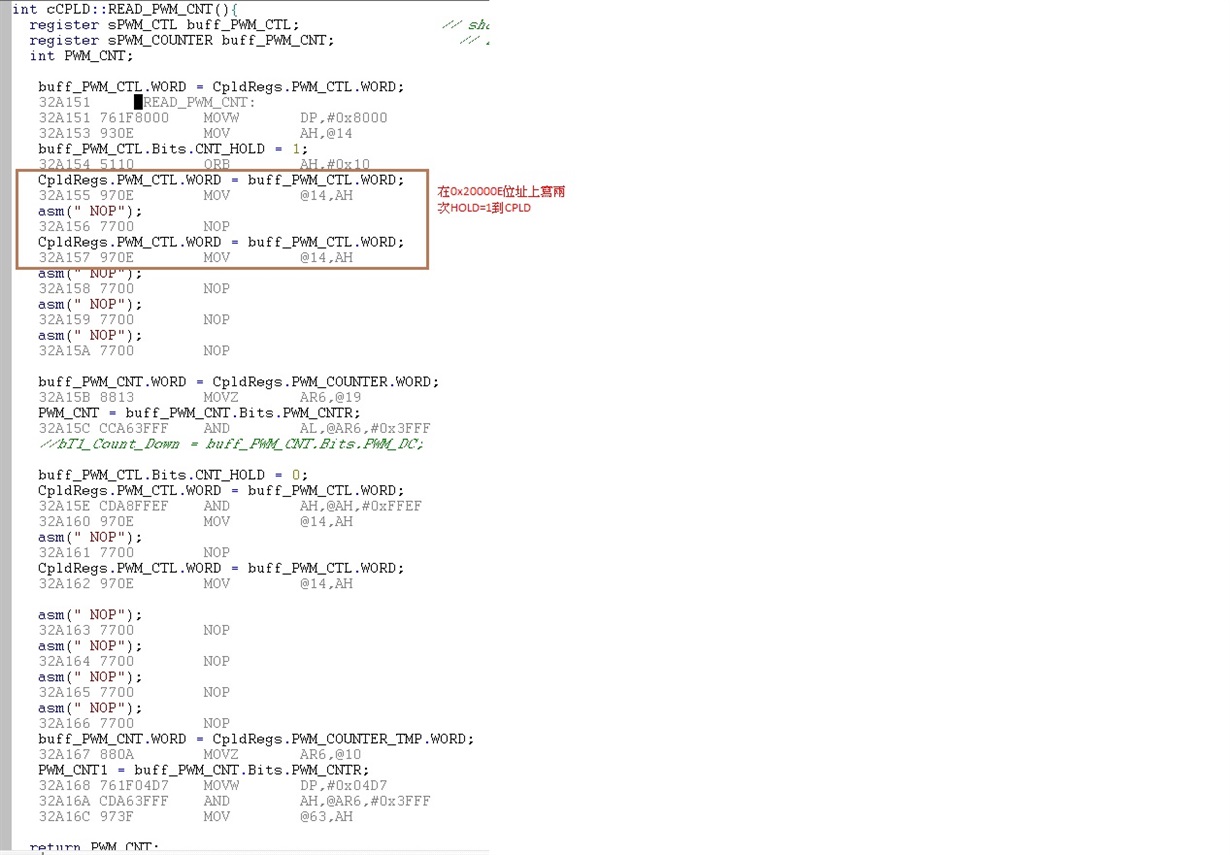

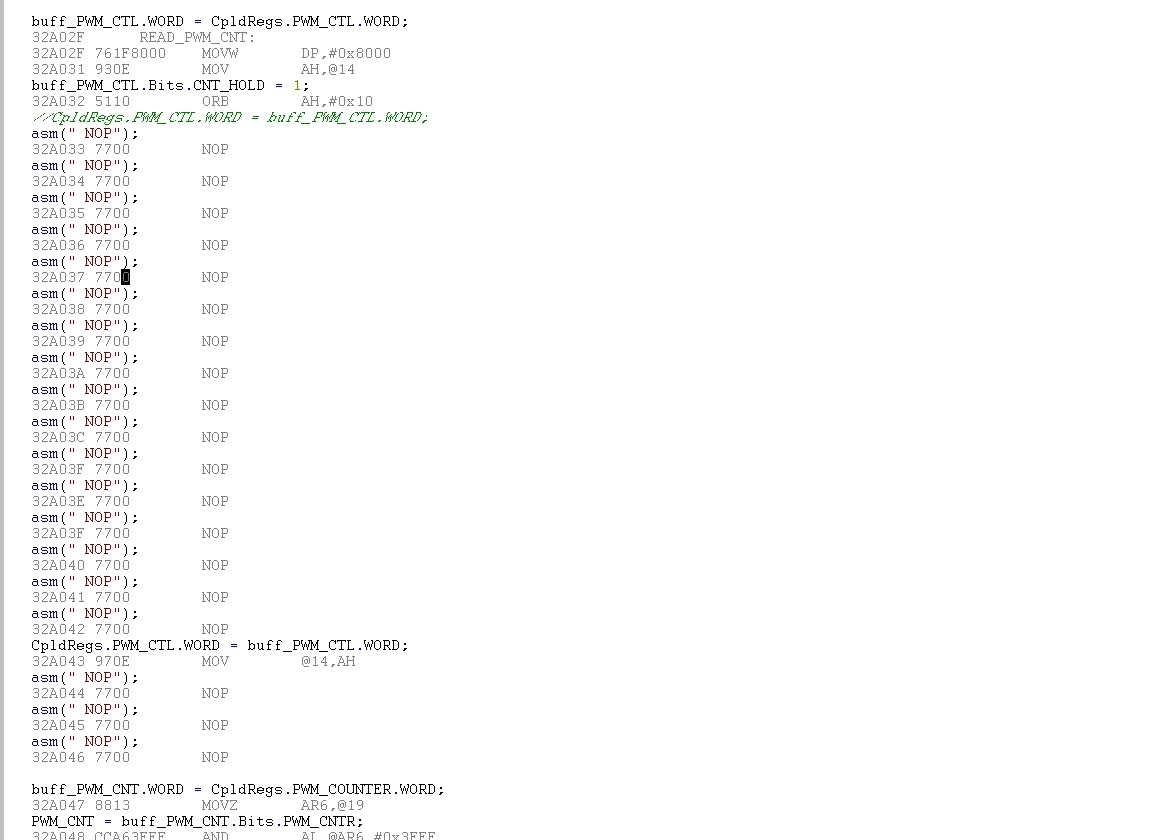

-----------<Below is the fail code >--------------------------------------------------------------------------------------

register sPWM_CTL buff_PWM_CTL;

register sPWM_COUNTER buff_PWM_CNT;

int PWM_CNT;

buff_PWM_CTL.WORD = CpldRegs.PWM_CTL.WORD;

buff_PWM_CTL.Bits.CNT_HOLD = 1;

CpldRegs.PWM_CTL.WORD = buff_PWM_CTL.WORD; <---write HOLD=1 to CPLD at 0x20000E address

buff_PWM_CNT.WORD = CpldRegs.PWM_COUNTER.WORD;

PWM_CNT = buff_PWM_CNT.Bits.PWM_CNTR;

buff_PWM_CTL.Bits.CNT_HOLD = 0;

CpldRegs.PWM_CTL.WORD = buff_PWM_CTL.WORD;

----------------------------------------------------------------------------------

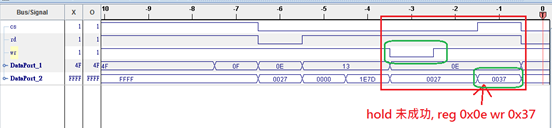

The fail code wave form: (hold not successful , reg 0x0e Wr 0x37)

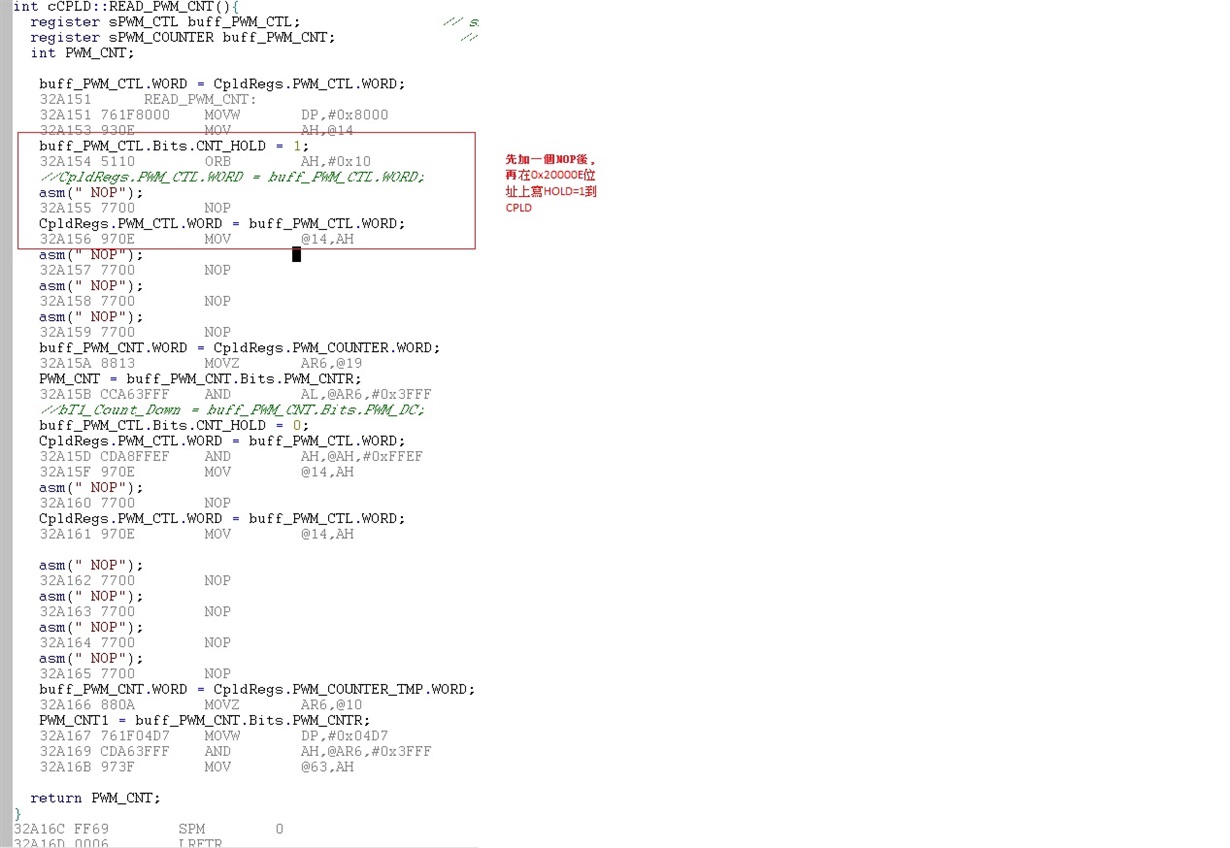

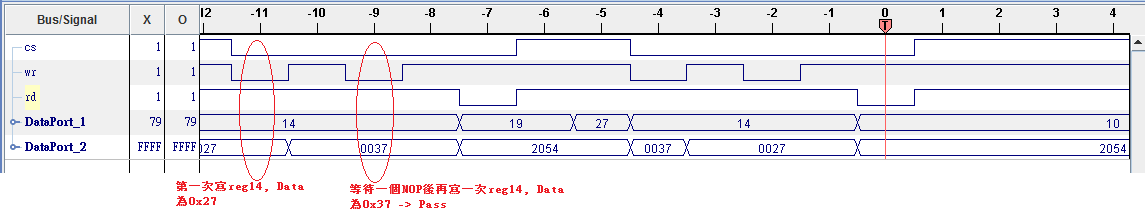

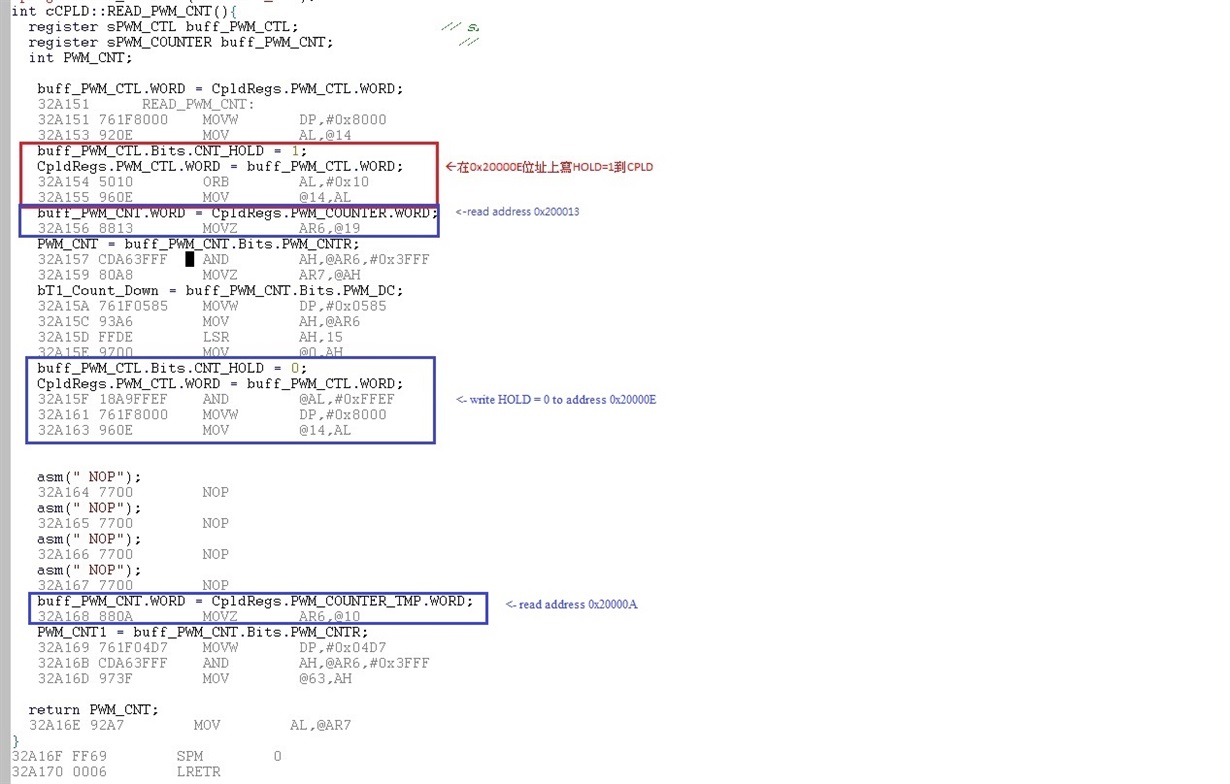

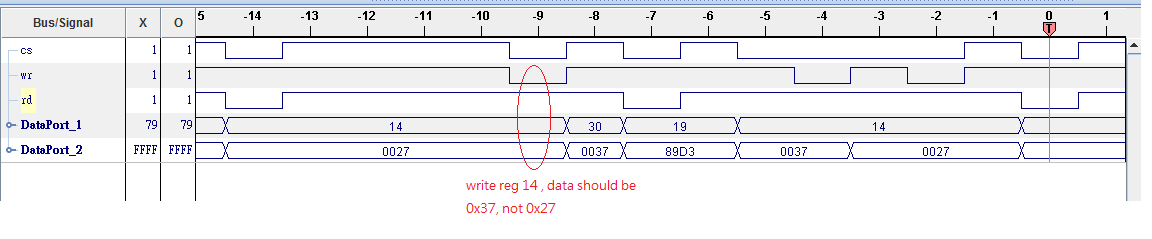

-----------<Below is the successful code >--------------------------------------------------------------------------------------

register sPWM_CTL buff_PWM_CTL;

register sPWM_COUNTER buff_PWM_CNT;

int PWM_CNT;

buff_PWM_CTL.WORD = CpldRegs.PWM_CTL.WORD;

buff_PWM_CTL.Bits.CNT_HOLD = 1;

CpldRegs.PWM_CTL.WORD = buff_PWM_CTL.WORD;

asm(" NOP");

CpldRegs.PWM_CTL.WORD = buff_PWM_CTL.WORD; <---write HOLD=1 to CPLD at 0x20000E address , and it is successful

asm(" NOP");

asm(" NOP");

asm(" NOP");

buff_PWM_CNT.WORD = CpldRegs.PWM_COUNTER.WORD;

PWM_CNT = buff_PWM_CNT.Bits.PWM_CNTR;

buff_PWM_CTL.Bits.CNT_HOLD = 0;

CpldRegs.PWM_CTL.WORD = buff_PWM_CTL.WORD;

asm(" NOP");

CpldRegs.PWM_CTL.WORD = buff_PWM_CTL.WORD;