Other Parts Discussed in Thread: TIDA-00915

Tool/software: Code Composer Studio

Hello, TI Engineer:

Recently read the "Three-Phase High PWM Frequency GaN Inverter Design TIDA-00915 Reference" reference design. There are some details about the high speed circuit inside. Do not understand, please point out.

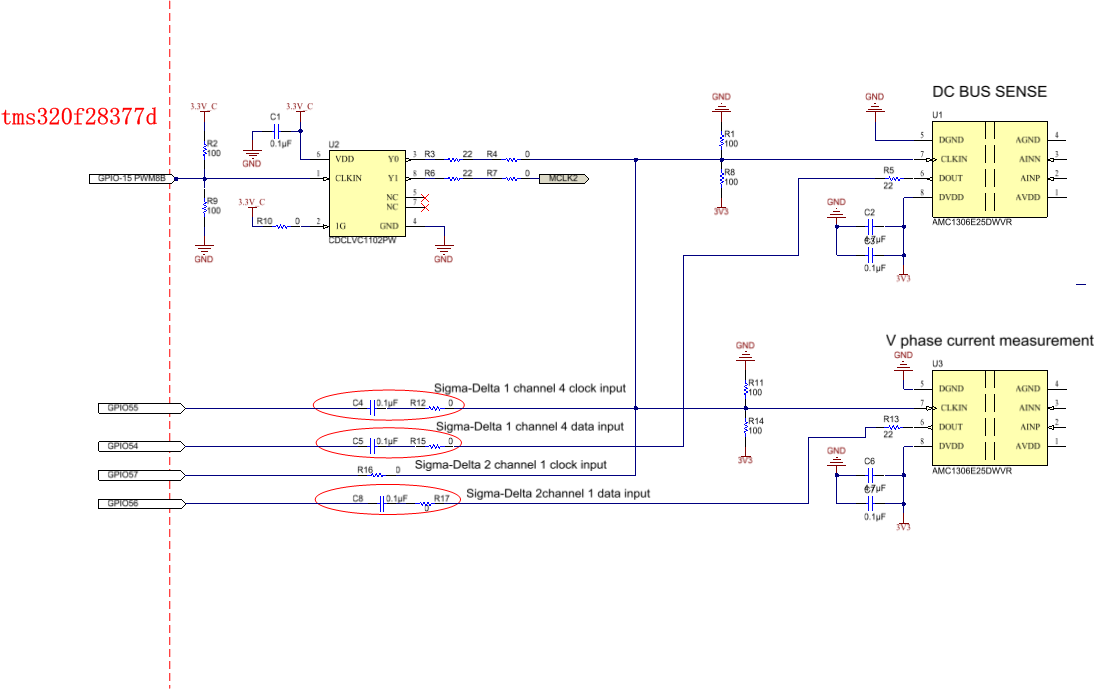

The circuit diagram is shown below. Tms320f28377d's "PWM output" serves as the clock signal(20.0MHz), providing the clock signal via buffer (CDCLVC1102PW) for 4 Sigma-Delta ADC converters (only 2 painted in the picture). The designers consider impedance matching, parallel two 100 ohm and series 22 ohm resistors to realize impedance matching. But why would a 0.1uF capacitor be connected in series between the CLK line and the DATA line?

I have four questions:

1.Is the impedance matching required to connect the 0.1uF capacitor to the CLK line and the data line? How is capacitive capacitance calculated? Can you recommend a document?Not all of the designers are connected to the 0.1uF capacitor, You can see,the DC bus voltage measurement of the CLK is not connect ed. Is it missing or something else?

2.Designers are connected in series with 0 ohm resistance, which is needed for debugging. (28377 Sigma-Delta ADC mode 2 can not use clock signal), or are there other reasons? How many 0 ohm resistances are connected in series so that they don't worry about impedance matching?

3.About when do you need to consider impedance matching? Some documents say that for 20MHz signals, PCB traces more than 50mm to consider. Another document says that the rising edge and the falling edge of the signal are less than 6 times the signal delay needed to be considered. Do you have any suggestions for when to consider? Because the TI reference circuit "uses the SAR and sigma delta ADC as a reference design for integrated diagnostic functions in protective relays, TIDA-00810" does not consider impedance matching in the same circuit.

4.How to evaluate CDCLVC1102PW's drive capability, CDCLVC1102PW's CLK pin drives 4 slices of AMC1306, and also provides clock signals for at least four Sigma-Delta ADC converters on tms320f28377d chips.

At this site, you can download the circuit diagram