I just ran into this weird situation. I wrote my code and tested it with 1MHz sine wave input and the result was good. But when I changed the input to 100KHz sine wave, the ADC plot is really bad.

So I switched back to the example code "adc_ex2_soc_epwm.c" and tested it. It has the same problem. I will attach some graph I obtained from my tests:

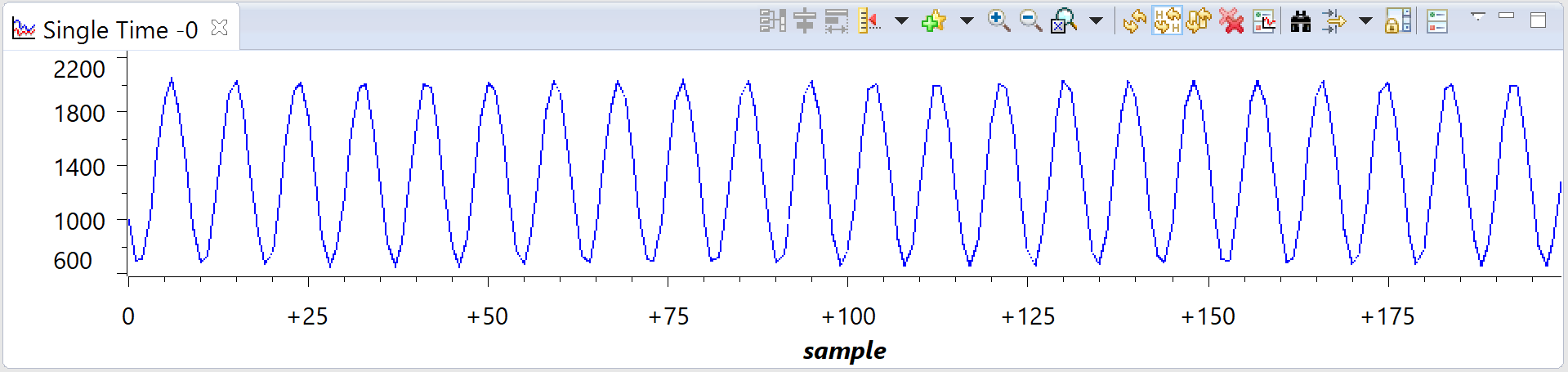

1st plot: 1MHz sine wave, 1Vpp, 1V DC offset

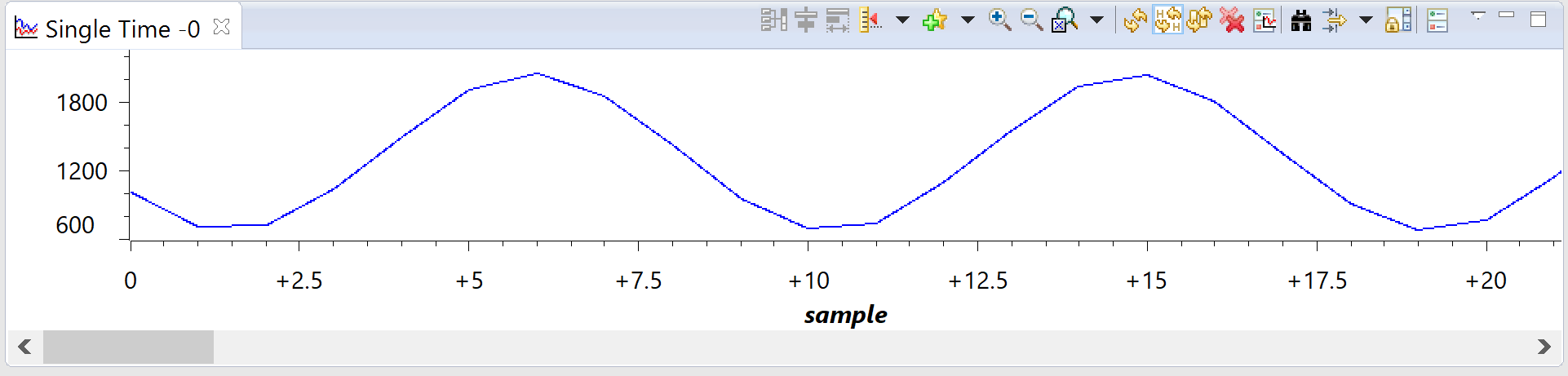

2nd plot: 1st plot zoomed in

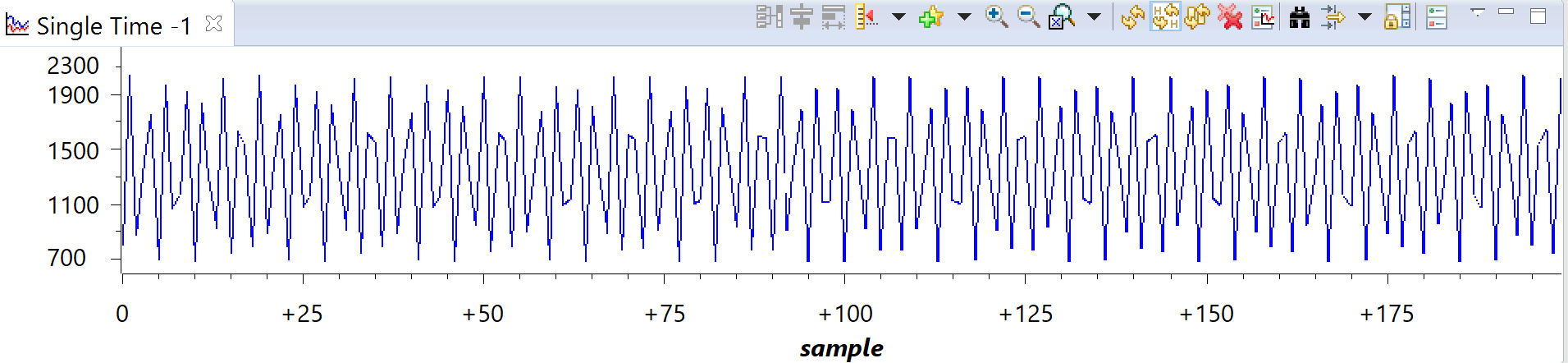

3rd plot: 100KHz sine wave, 1Vpp, 1V DC offset

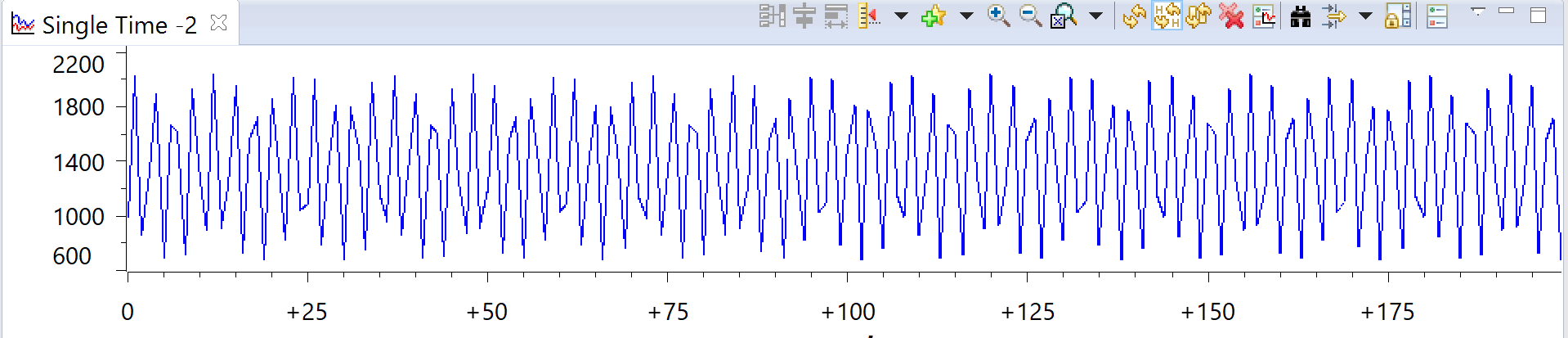

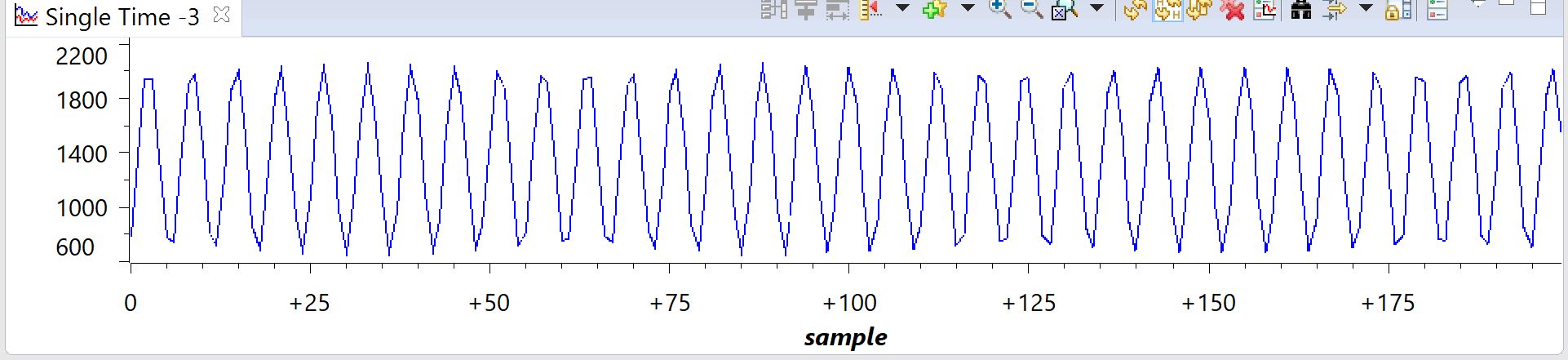

4th plot: 10KHz sine wave, 1Vpp, 1V DC offset

5th plot: 1KHz sine wave, 1Vpp, 1V DC offset

I don't understand why the ADC can sample 1MHz nicely but it cannot handle 100KHz and 10KHz.

another problem I don't get understand is: when I sampled 1MHz, I can get around 8 samples per cycle (so it's like 8MSPS), but I only got about 5 samples per cycle when I sampled 1KHz (so it's like 5KSPS).

I don't know if my method to calculate ADC sampling rate is correct.