Other Parts Discussed in Thread: CONTROLSUITE, C2000WARE

Tool/software: Code Composer Studio

Hello,

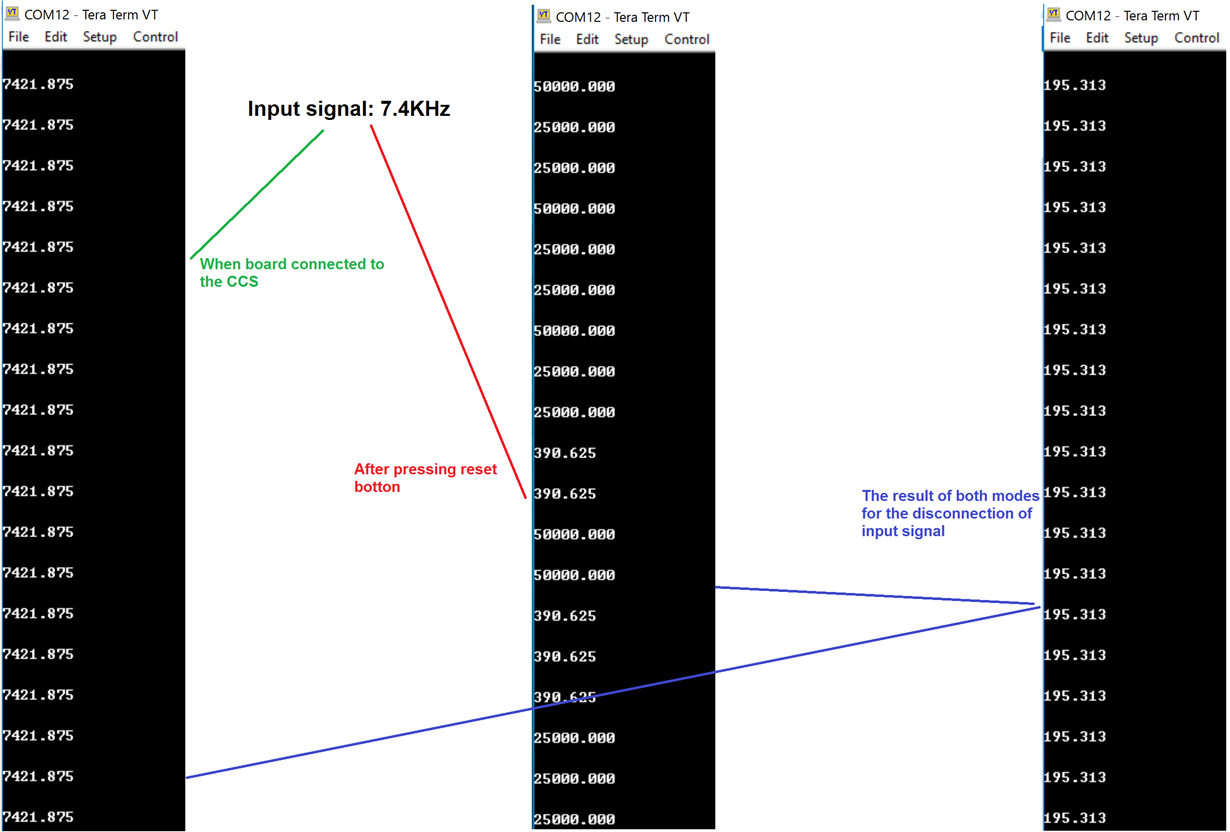

I am using the “2837x_rfft_adc_rt” examples provided by TI, the program is working fine and all the results(ADC input/fft values) are good when I build and load to the FLASH mode(Build Configurations -> Set Active -> Select FLASH_FASTRTS(…) ) using CCS, when board is connected to the CCS.

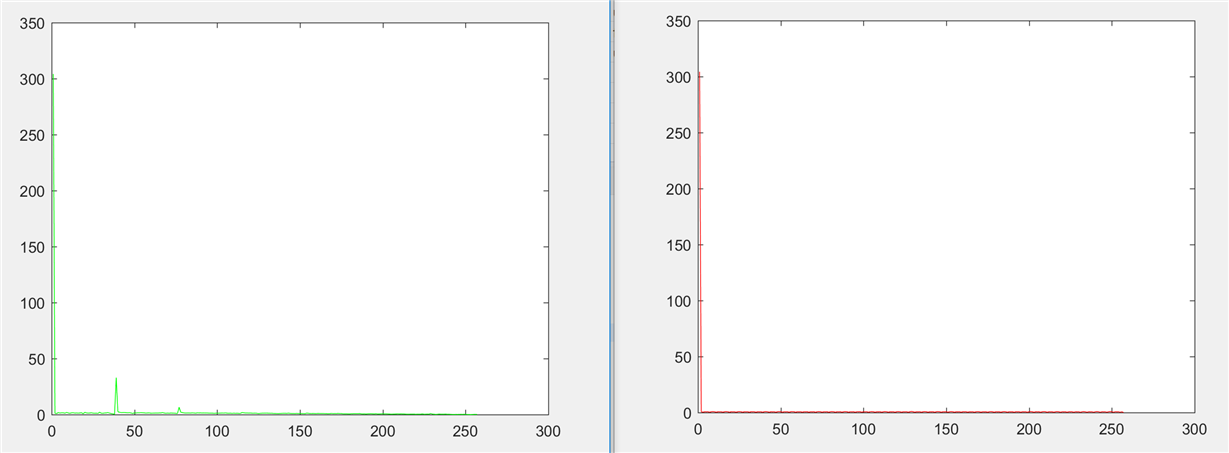

If I reconnect the board from my PC, program does not work completely (I can see the correct ADC input signal, but, FFTmagBuff[] does not work. In the other words, the Fourier transform seems to be taken, but its value is not correct and the results are wrong). The green graph(FFTmagBuff-correct result) is for the case where the launchpad is connected to the CCS and started to work by code composer studio. The red graph(results of FFTmagBuff are wrong) is for the case where the rest button of the board is pressed.

Thanks for your help.

Regards,

Amin