Tool/software: TI-RTOS

Dear T.I. forum followers,

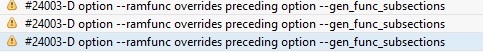

Recently I've been working on transferring my code which was operating on RAM to a standalone application running on Flash on F28069M, In a better word, I had an application working totally fine on RAM, then for flashing it, I used --ramfunc attribute to copy the whole application from Flash to RAM in the beginning of the operation. Using the help of you guys in here I succeed and now I have a code running from Flash but the issue I'm facing now is that the performance of my code after flashing is not identical to RAM which is super critical in my application, I mean the application on the RAM works with 100% consistency of responses, but the application from Flash (copied to RAM in the beginning ) works with almost 85% of consistency. I used the initFlash() function in the beginning of my main() which improved a lot the performance but still the performances are not identical.

What I'm wondering now is what is the cause of this issue, I know that the Flash has some wait sates and it's not fast like RAM, but I'm coping the whole application in the RAM in the beginning, so what else can be the cause of the problem?

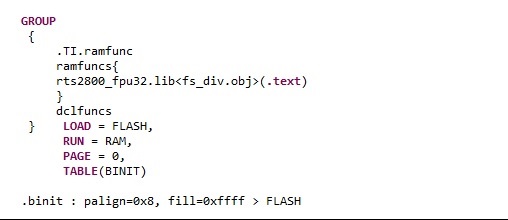

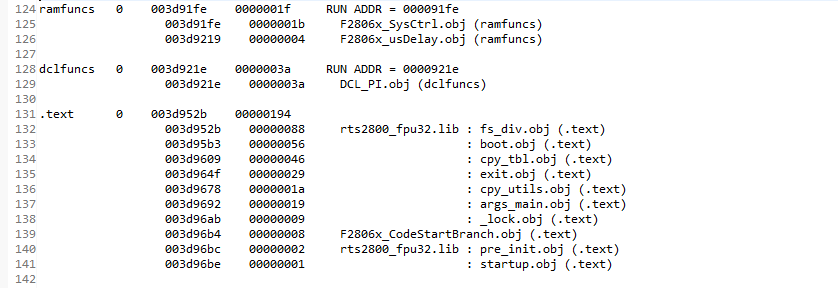

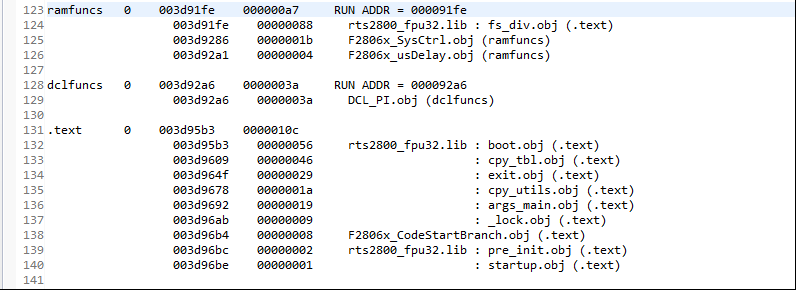

To help you to solve my issue I've attached the .map file generated using my linker command file and also the linker command file itself.

Thanks in advance

Milad