Customer encountering a strange issue in the code, I’m not sure exactly what is the root-cause.

- Attached is my Linker File: F28035_issue.zip

- I have “.ebss : >> M0M1_DRAM | L0_DRAM | L1_DRAM, PAGE = 1”

- Split my variables across available RAM

- F2_APP_RLS_NoNewVar.Map à This is the “before” state when everything is working.

- I confirm working by stepping through the code: ptrBboxRam = (Uint16 *)(&sBboxRam);

- In the Map File, see Line 766. sBboxRam is located in 0x8540 (in L0 SARAM). When I step-through the code, I can see that ptrBboxRam=0x8540, and so I can confirm that the pointer has the correct value.

- F2_APP_RLSWithNewVar à This is the “after” state when something is wrong.

- I added a new variable sSnapLocal, an array with 62 words. This new variable is in 0x8840 (in L1 DPSARAM)

- Adding this new variable also caused sBboxRam to be relocated to 0x8900 (in L1 DPSARAM)

- When I step-through the code, I get ptrBboxRam=0xC1A1C7F7. It is a crazy high number out of the memory range so I know something is wrong.

- If I comment-out the declaration of sSnapLocal, re-compile and run, then code is working again because ptrBboxRam gets the correct value.

- So I have confirmed that the error has something to do with this new variable. And I’m suspecting it is because sBboxRam has been relocated from L0_SARAM to L1_DPSARAM. I have the impression that all RAM memories in this DSP are “similar” except L0 is dual-access.

- Attached also is my Makefile so you can review my compiler/linker settings.

At the moment, I’m struggling to understand what could be the reason, might be a simple checkbox in the compiler options or more complicated. I am currently adding a feature called “blackbox” and it is quite memory intensive. sBoxRam itself has 672 words.

However, if I combine Mo, M1, L0, L1 all together, there is still enough space to go, so I know I’m not running out of space (yet) so maybe this is only a setting issue.

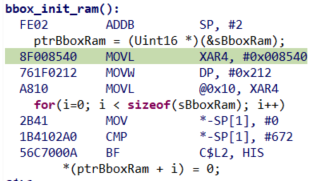

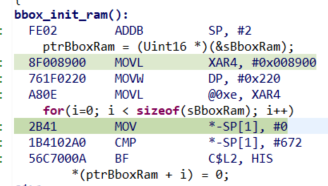

Customer tried to compare the Disassembly code, see pics below. The code looks pretty similar, obviously except for the different memory address and DP value.

“Before” state sBboxRam @ 0x8540

“After” state sBboxRam @ 0x8900

I hope you can guide me on this one.

Regards, Bernd