Other Parts Discussed in Thread: CONTROLSUITE

Tool/software: Code Composer Studio

Dear C2000 experts,

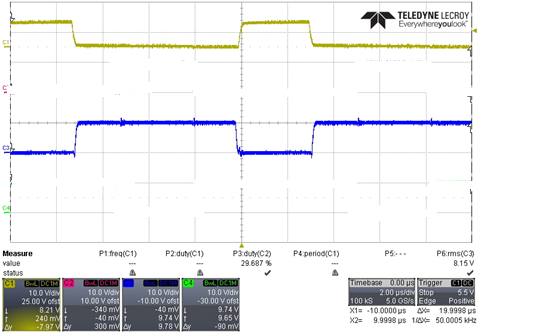

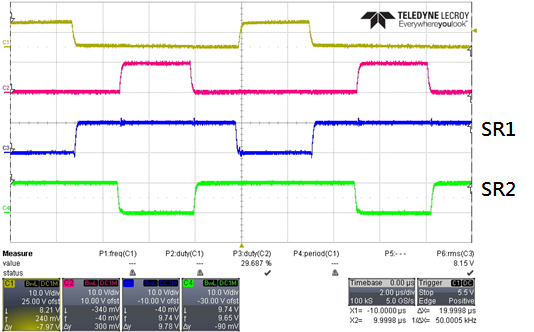

I'm using the F28035 to develop a buck converter with the synchronous rectifier and there is a dead time between the MOS switches. The topology I choose is the Hard-Switching Full-Bridege and the control method is the peak current mode control. I can generate the 1st side MOS control with the TZ function with the comparator, but cannot get the correct waveform of 2nd side SR MOS. The figure below is the waveform I would like to generate. The yellow one is the 1st side waveform and the blue one is the SR waveform.

Is there any sample code that I can refer?

Many thanks for the help.

Young