Other Parts Discussed in Thread: INA240

Having discovered some part of precision error ADC0 was related to periodic analog signal triggered sample step POP's into specific array cells are zero. The digital conversion of the actual value is near 2mV analog signal yet 0x0000 was sampled.

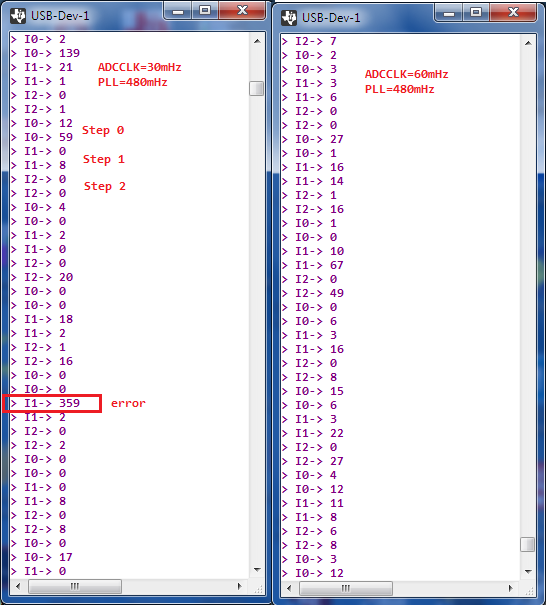

Speeding up ADCCLK to what is believed to be 60mHz with supposedly 480mHz PLL improves ADC sample acquisition precision. How can precision increase beyond the 2MSPS if ADCCLK being 30mHz or even 60mHz is acquisitioning far to many 0x0000 in numerous samples? The analog signal has very clean acquisition points. When sequencer is triggered via GPTM the AD converter appears to produce finer acquisition granularity locking on analog signal than being triggered via PWM0 GEN0 that is producing 80us analog signal peaks being sampled. Also the values being POP into array cells only slope the steady state signal up to a threshold (200mA) being 2mV but refuses to slope below that VREFP-VREFN value of previous POPs even though the initial slope is positive from 0v up to 2mV. If a cheap 6000 count 1.2kHz DMM can easily measure this same current (up/down) scale surly the TM4C precision ADC can easy as pie, right? This DMM by no means has such a precision ADC the TM4C is touted to have, so there must be something gone all wrong in sequencer configuration.

ADCSSFSTAT TPTR index alignment to actual POP of FIFO data has no effect to improve missing acquisitions 0x0 below. AD converter should never produce full strings of 0x0 after or during the analog signal approaching and then reaching steady state, right? AD conversion actually starts out by producing a heck of lot more strings of 0's than shown below.

It seems there is a timing issue with SYSCLK and ADCCLK being in different time domains even though supposedly VCO is producing both clocks plus the 60Mhz PWMCLK. How can a 60mHz ADCCLK even be possible without raising MCU temperature from overclocking ADC module yet here it is in the diagram below?