Hi,

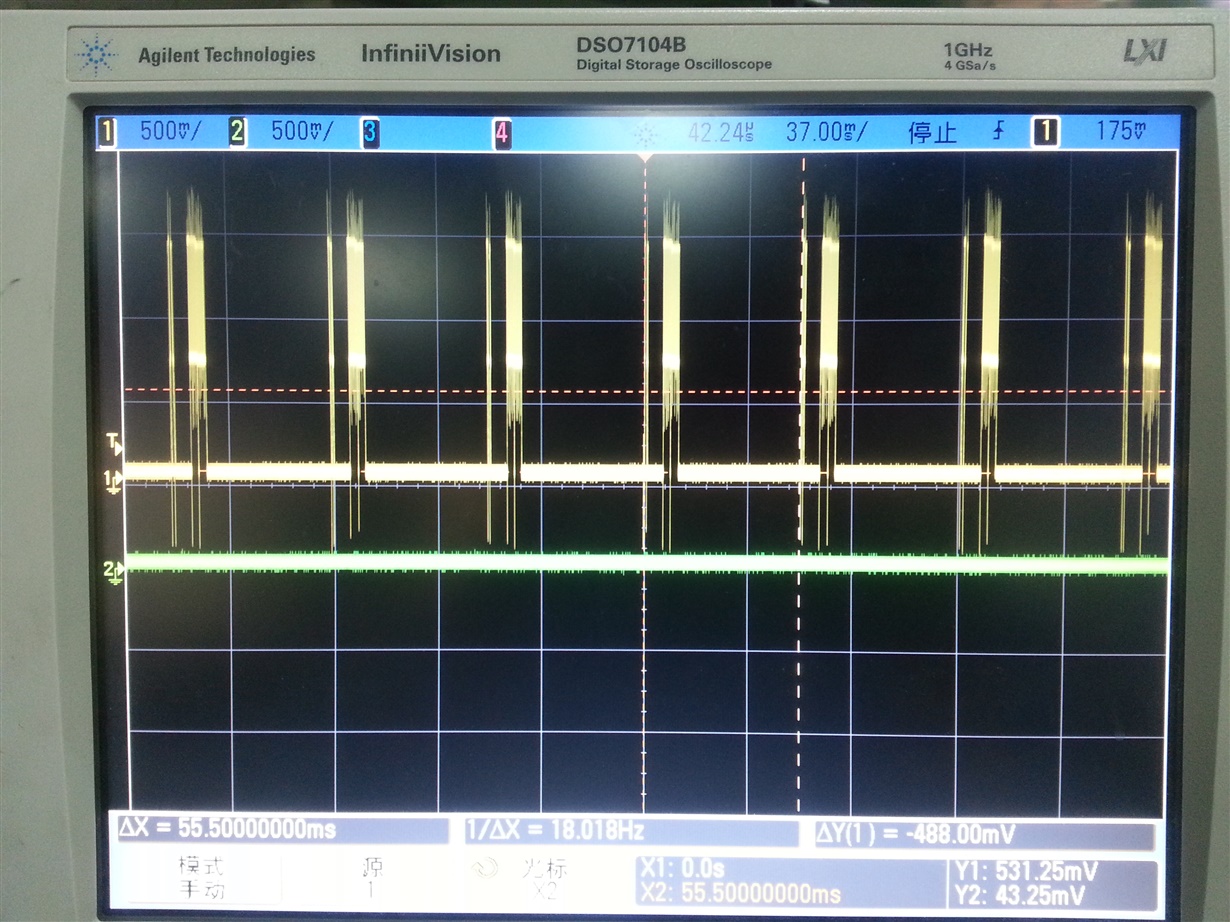

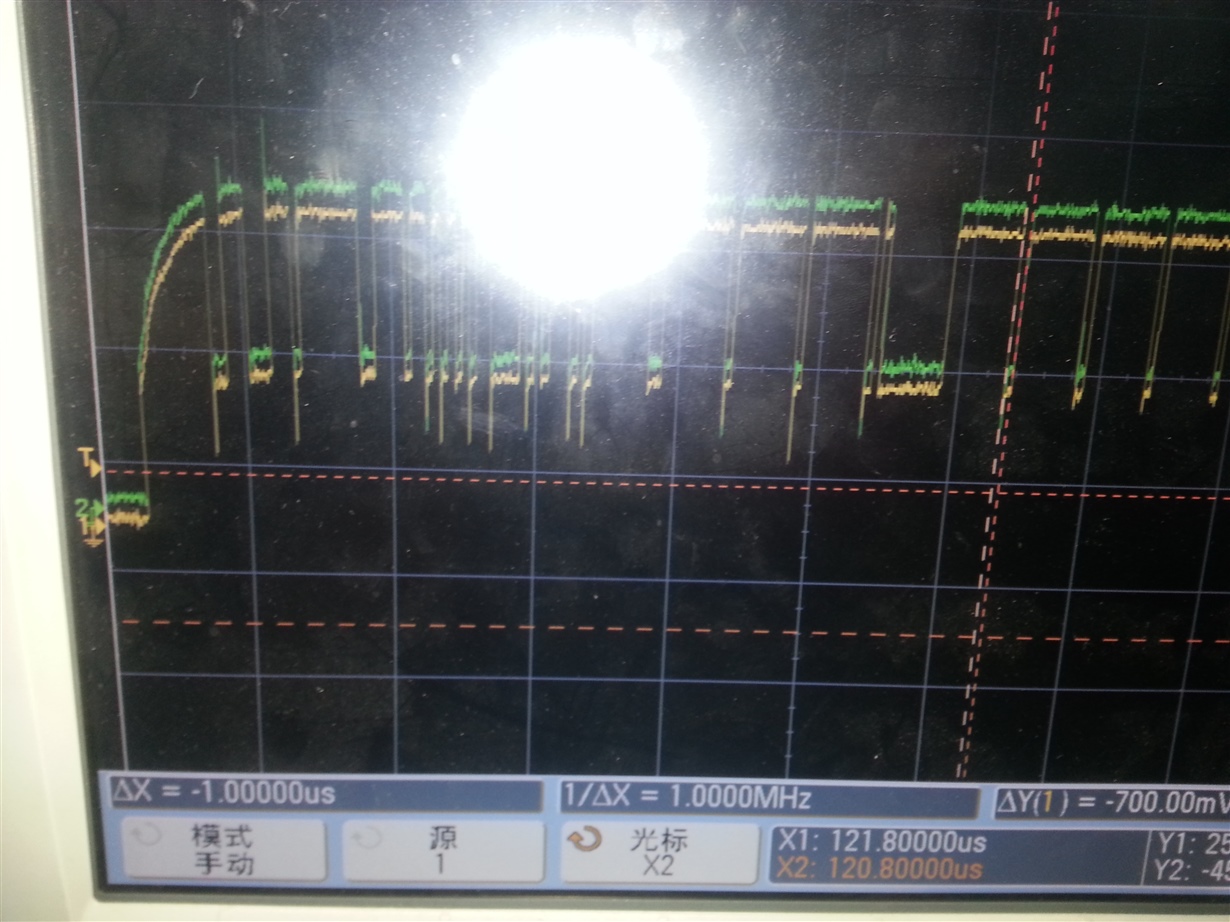

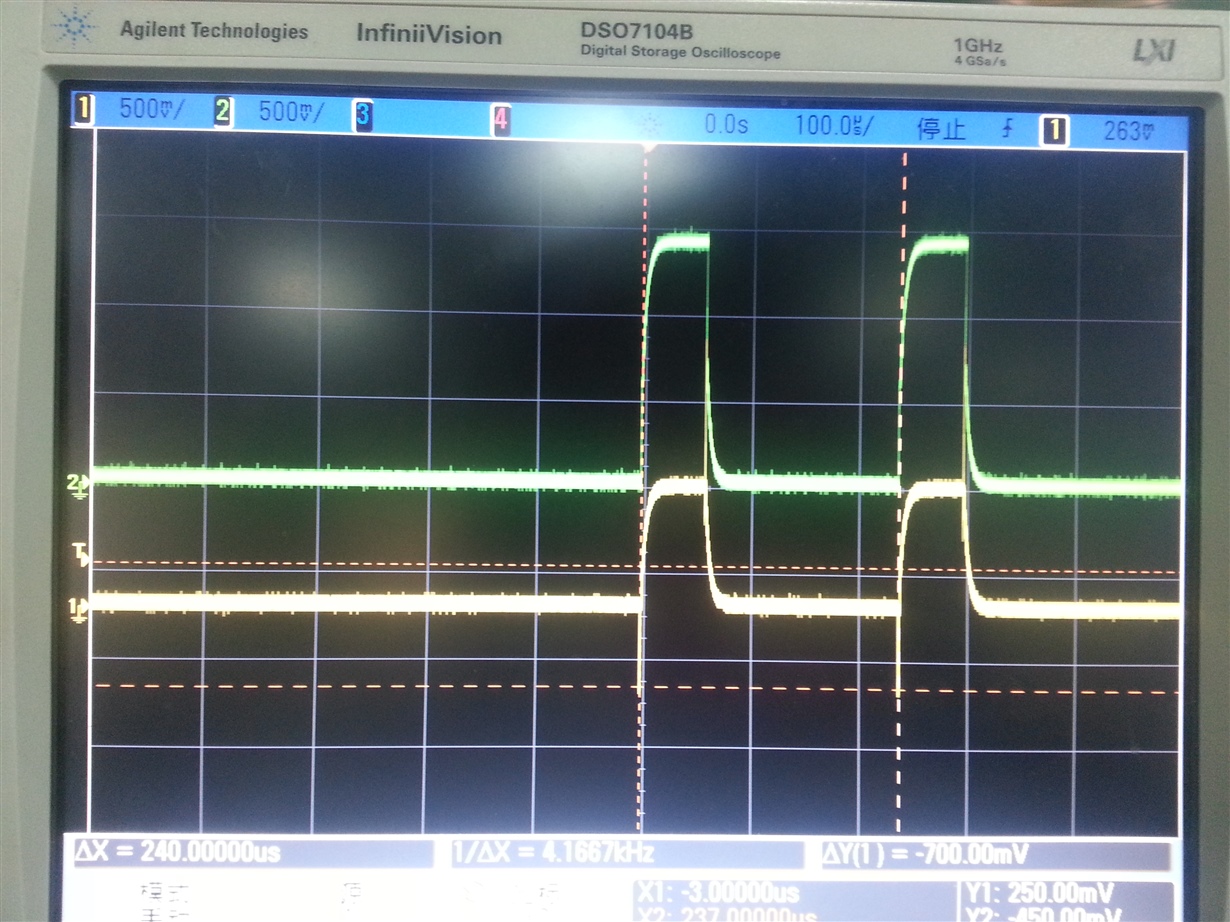

The attatched pictures are the singles I probed on the transition line, including the cycle, bit length, configuration and wakeup pattern.

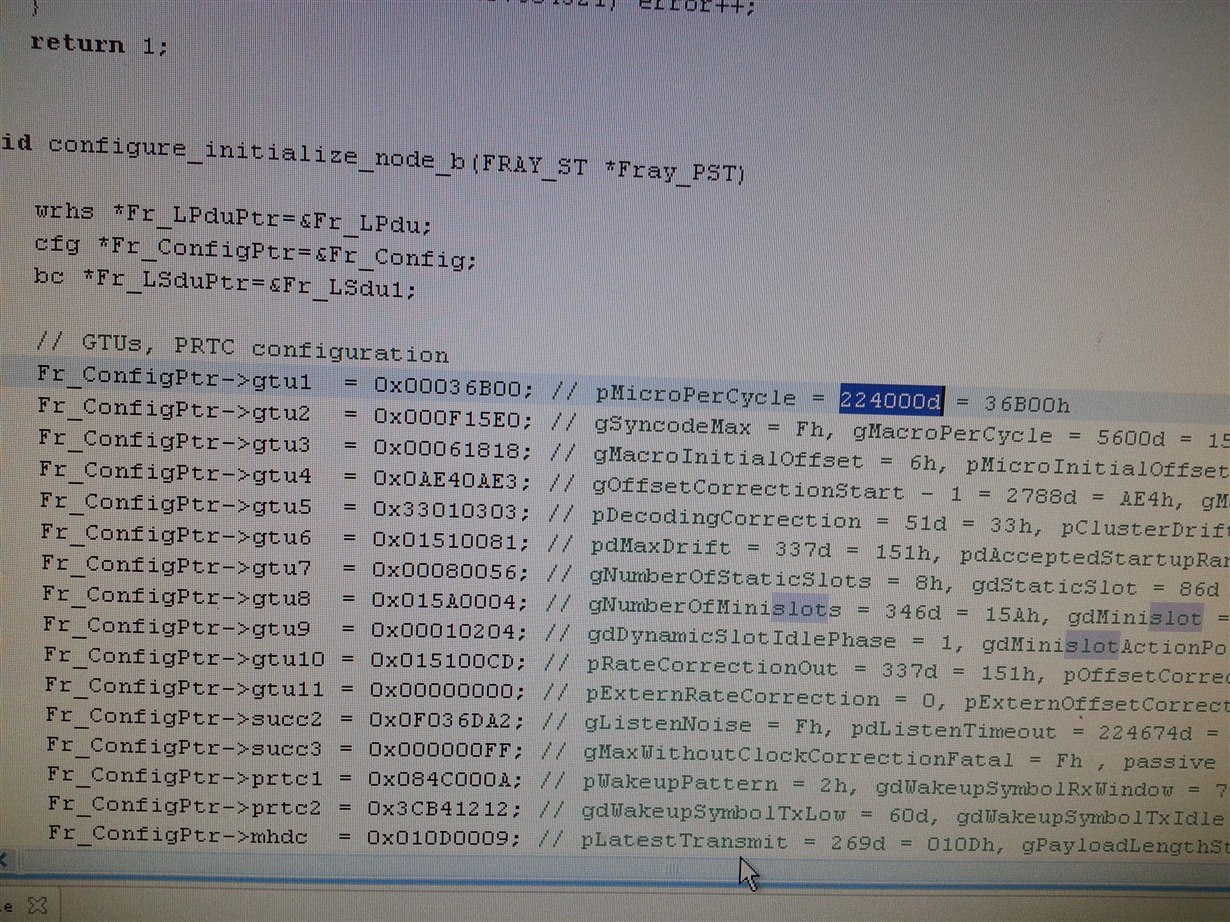

According to the configuration in the example, pMicroPerCycle=24000d, bit rate=10Mbit/s(PRTC1.BPR[2]=0X0), namely 4uT=100ns, thus the cycle length should be 5.6ms. However, the actually cycle length I test is 56ms.

I am wondering why the cycle length is as ten times long as I expected.

Also, in the two node FlexRay example, the lcb, ffb and fdb in the mrc register are set as 23, 64 and 4 respectively. According to the mannual, the controller can only use the message ram buffers numbered less than lcb. Thus, I supporse the wrhs3.dp should be configured with a number less than lcb(23) and more than 0. However, in the example, for different frames the wrhs3.dp(s) are set as 0x80, 0x84, 0x200 which are all more than lcb value. I would appreciate if you could explain the reason for this.

Waiting for your response

Best Regards,

Liu Xuan