Hi TI,

I am using TMS570LC43x HDK with free-RTOS implemented. In this, I created 5ms Task.

unsigned int temp_arr [5000] __attribute__((section(".sdram"))) , temp_var1 __attribute__((section(".sdram"))) ,temp_var2 __attribute__((section(".sdram"))) ;

void _5msTask(void *pvParameters)

{ temp_var1=temp_var2=0;

while(1)

{

gioToggleBit(gioPORTA,1); // On time = 5ms, Off time =5ms (Expected)

gioSetBit(gioPORTA, 2, 0); // GIOA.2 Low time is Execution time.

for(temp_var1 = 0; temp_var1<5000;temp_var1++)

{

temp_arr[temp_var1] = temp_var2;

}

gioSetBit(gioPORTA, 2, 1);

vTask_PreEmp(5);

}

}

So when executing the code I don't get the result as expected.

GIOA.1 On time = 9.1ms, GIOA.1 Off time = 9ms and

GIOA.2 Low pulse time = 4.91 ms (Execution time).

So my 5ms Task is not working properly.

But When I am moving variables from SDRAM to internal RAM as below,

unsigned int temp_arr [5000] __attribute__((section(".ram"))) , temp_var1 __attribute__((section(".ram"))) ,temp_var2 __attribute__((section(".ram"))) ;

I obtain output as expected.

GIOA.1 On time = 5ms, GIOA.1 Off time = 5ms and

GIOA.2 Low pulse time = 407 us (Execution time).

So when I use External SDRAM my controller is 12 times slower.

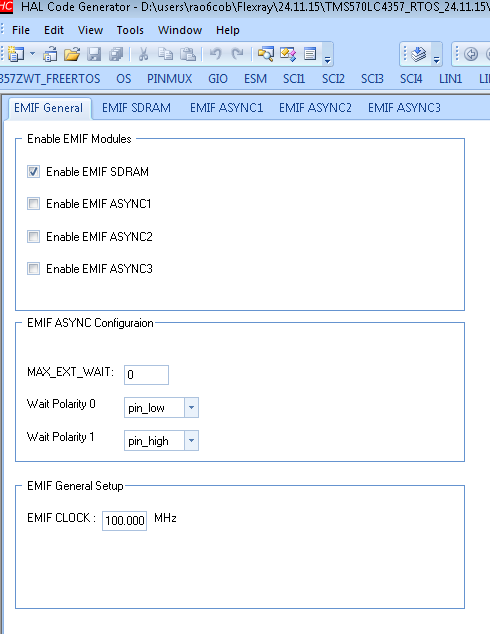

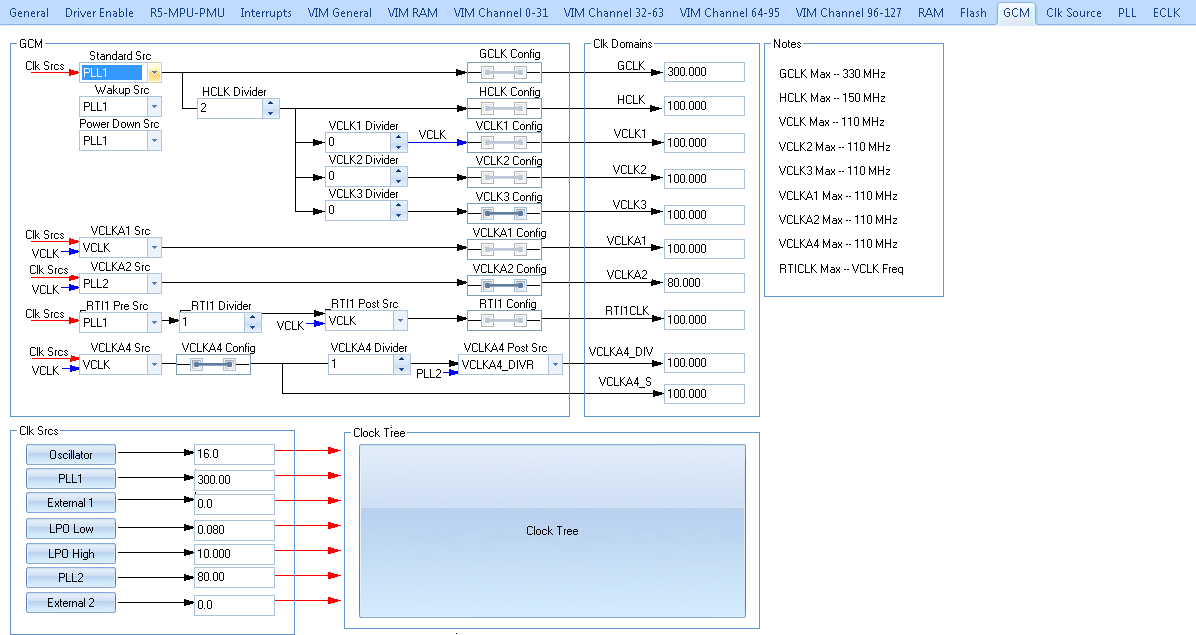

I have given my SDRAM halcogen settings below.

So why External SDRAM access takes 12 times slower than, internal RAM Access.?

How to decrease the access time to SDRAM?

Does my configuration settings is proper? Please guide me a solution.

Thanks in advance.

Regards,

Joel.