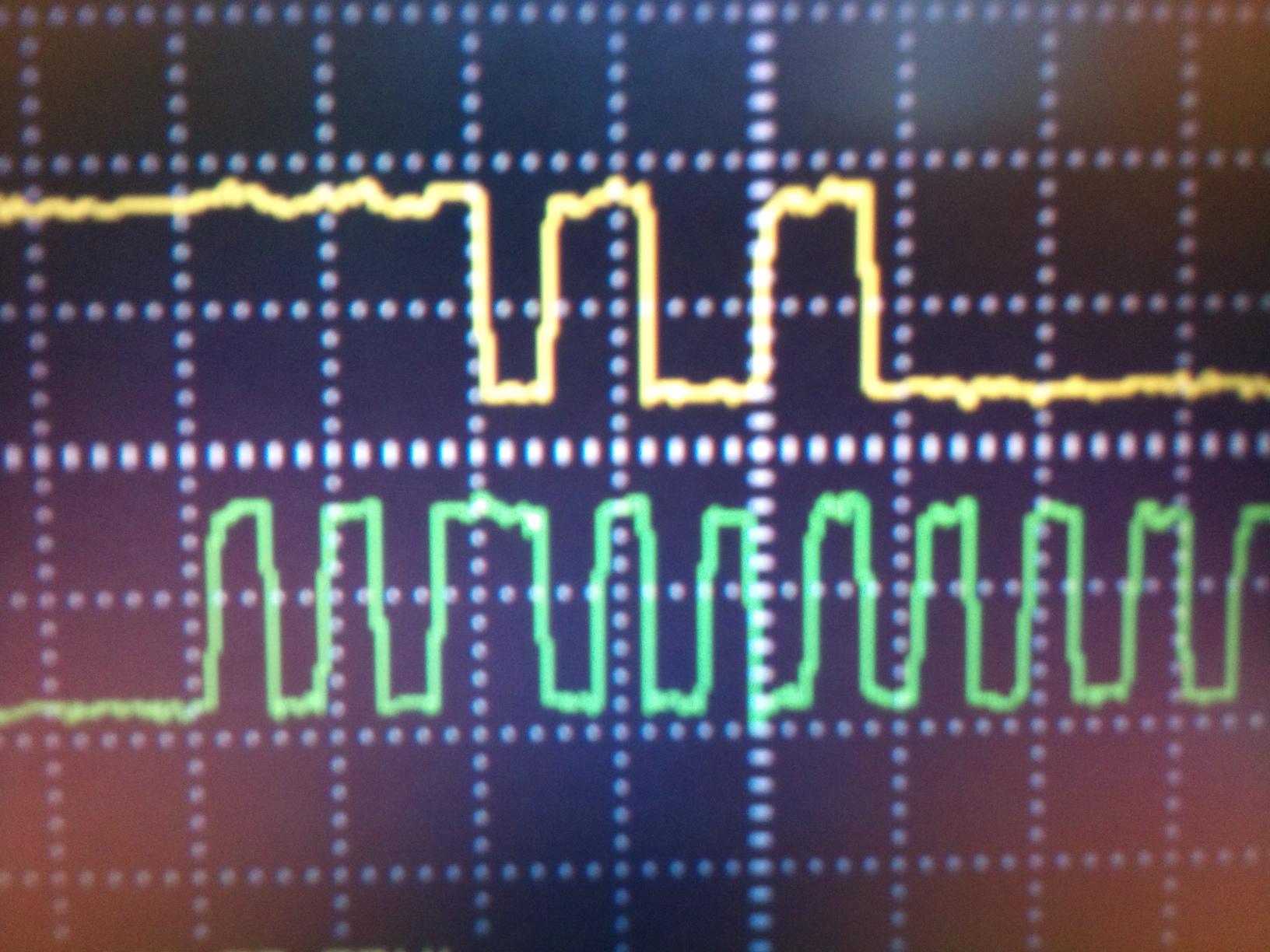

I'm trying to put the i2c device to work but the busy flag is always set. Checking the lines on the scope, both are high SCL and SDA. As soon the UCB0 config is done, the UCBUSY goes to Hi. What should it happening? Its configured as master, sync mode, by Smclk/11.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.