Hi Sir,

I am using MSP430g2231 microcontroller to generate a clock frequency of 38kHz in one of the GPIO pin(P1.4).

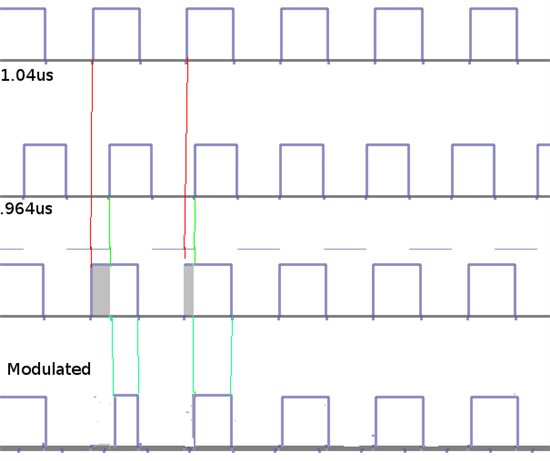

That means I am trying to generate a clock cycle pulses of period "26micro seconds"(1/38khz). I have used the

configurations and written the code as shown below. The problem that I am facing is, when I am trying to check

the result in oscilloscope the cycle period varies in between 32, 34 and 38 micro seconds. So my question is

what am I doing wrong with my code? Is there any wrong with my clock selection..since I am using calibrated

clock (internal) values of 1Mhz or I am doing wrong in setting values of TimerA CCR0 value? Please provide the

support and help. Thanks.

#include "msp430g2231.h"

void main(void) {

WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer

if (CALBC1_1MHZ ==0xFF || CALDCO_1MHZ == 0xFF)

{

while(1); // If calibration constants erased

// do not load, trap CPU!!

}

DCOCTL=CALDCO_1MHZ;

BCSCTL1 =CALBC1_1MHZ;

//make Port pin 4 as output*/

P1DIR = BIT4;

P1OUT = 0x00;

configureTimer();

__enable_interrupt();

while(1);

}

/*I am trying to generate each pulse duration 13us*/

void configureTimer()

{

CCR0 = 13-1; // set up terminal count

TA0CTL = TASSEL_2 + ID_0 + MC_1; // SMCLK + SMCLK/1 +up mode

// enable interrupts

CCTL0 = CCIE; // enable timer interrupts

}

//Toggling the pin 1.4

#pragma vector = TIMERA0_VECTOR

__interrupt void Timer_A0_clkgen(void)

{

TA0CCTL0 &= ~CCIFG;

P1OUT ^= BIT4;

}