Hello,

I am using the mspf5438a, with CCS 5.3. and the linker is data type is of eabi.

And in my code i write data to address 0x10000 (to the flash, and above the lowest 64k).

Therefore, I presumed that I should use the data memory model = large,

And to stay with the code memory model = small.

I saw that the program don’t work ( the writing to the memory was failed) . I check with the debugger and saw that:

the data pointer to the flash (unsigned long * Flash_ptr ) is just 16 bit ( and not 32 ) and that the reason that the data is written to different address.

I try to make change , and change the memory model to “code memory model = large” , and it solve the problem ( the data pointer change to 32 bit and cover the whole address space). But instead I get the following warnings:

#70-D integer conversion resulted in truncation

#770-D conversion from pointer to smaller integer

and the warnings is related to the following line code:

__data16_write_addr((undigned short)&DMA0SA, (unsigned long)&UCA0RXBUF);

But still I was left with a lack of clarity in relation to the written code. And have a few questions that I want to understand.

- why , working with the “data memory model = large,and code memory model = small” , not work? And the unsigned long * Flash_ptr , was just with 16bit size ( and therefore point to the lowest 64k memory ) and not 32 bit ( like I had expected for large data memory model) .

- why changing to “code memory model = large” solve the problem? I have no code in the address above the lowest 64k memory. My code memory model should be small.

- what the meaning of the warnings that I get ( when i change to large code memory model) ? After all , The address of the registers ( which the warnings related to ) is not changed and stay in the lowest 64k.

is any one have a hint or answers ??

thanks .

Asher.

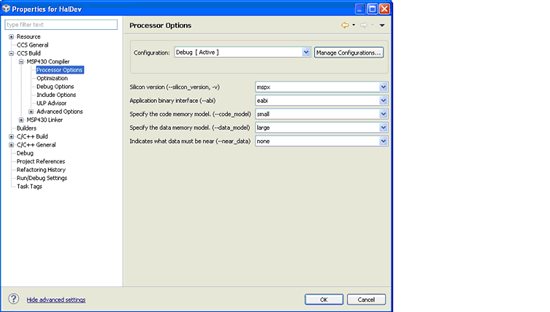

my configuration is:

Compiler:

-vmspx --abi=eabi --code_model=small --data_model=large --near_data=none -g --include_path="C:/ti/ccsv5/ccs_base/msp430/include" --include_path="C:/ti/ccsv5/tools/compiler/msp430_4.1.2/include" --include_path="../hdr" --advice:power="all,-2.1,-3.1,-5.2,-5.3,-8,8.1" --define=__MSP430F5438A__ --diag_warning=225 --display_error_number --silicon_errata=CPU21 --silicon_errata=CPU22 --silicon_errata=CPU40 --printf_support=full

Linker:

-vmspx --abi=eabi --code_model=small --data_model=large --near_data=none -g --advice:power="all,-2.1,-3.1,-5.2,-5.3,-8,8.1" --define=__MSP430F5438A__ --diag_warning=225 --display_error_number --silicon_errata=CPU21 --silicon_errata=CPU22 --silicon_errata=CPU40 --printf_support=full -z --stack_size=400 -m"HalDev.map" --heap_size=400 --use_hw_mpy=F5 -i"C:/ti/ccsv5/ccs_base/msp430/include" -i"C:/ti/ccsv5/tools/compiler/msp430_4.1.2/lib" -i"C:/ti/ccsv5/tools/compiler/msp430_4.1.2/include" --reread_libs --warn_sections --display_error_number --rom_model

i attach the following data:

1. picture of the configuration.

2. files:

source,

linker configuration file.

map file

/* ------------------------------------------------------------------------ */

/* Include Files */

/* ------------------------------------------------------------------------ */

#include <msp430.h>

#include <string.h>// for strlen(), memcpy();

#include "ig_def.h"

extern void ClockCnfg (void);

extern void TimerA1Cnfg (void);//system clock

extern void PortCnfg ( void );

/* ------------------------------------------------------------------------ */

/* Functions Body */

/* ------------------------------------------------------------------------ */

#define FLASH_MEM_BEGIN 0x5C00 // Flash code starting address

#define FLASH_MEM_LENGTH 0x0200 // Function segment size to be copied

#define RAM_MEM_BEGIN 0x1C00 // RAM code start

extern unsigned int flashcode_loadstart;

extern unsigned int flashcode_loadsize;

extern unsigned int flashcode_runstart;

void copy_flash_to_RAM(void);

void write_block_int(void);

unsigned long value;

int main(void)

{

Uint16 tmpCnt = 1;// cycle delay counter.

__bic_SR_register(GIE); // disable interrupt.

PortCnfg();

ClockCnfg();// 16mhz

TimerA1Cnfg();//timer interrupt of 10Hz.and blink the led

copy_flash_to_RAM(); // Copy flash to RAM function

value = 0; // initialize Value

write_block_int(); // This portion of code is executed in RAM

__bis_SR_register(GIE); // enable interrupts

while(1)

{

__no_operation();

}

}

//------------------------------------------------------------------------------

// Copy flash function to RAM.

//------------------------------------------------------------------------------

void copy_flash_to_RAM(void)

{

unsigned char *flash_start_ptr; // Initialize pointers

unsigned char *RAM_start_ptr;

//Initialize flash and ram start and end address

flash_start_ptr = (unsigned char *)FLASH_MEM_BEGIN;

RAM_start_ptr = (unsigned char *)RAM_MEM_BEGIN;

// Copy flash function to RAM

memcpy(RAM_start_ptr,flash_start_ptr,FLASH_MEM_LENGTH);

// memcpy(&flashcode_runstart, &flashcode_loadstart, flashcode_loadsize);

}

#pragma CODE_SECTION(write_block_int,".FLASHCODE")

//------------------------------------------------------------------------------

// This portion of the code is first stored in Flash and copied to RAM then

// finally executes from RAM.

//-------------------------------------------------------------------------------

void write_block_int(void)

{

unsigned int i;

unsigned long * Flash_ptr;

Flash_ptr = (unsigned long *)0x10000; // Initialize write address

// Flash_ptr = (unsigned long *)0x5E00;

__disable_interrupt(); // 5xx Workaround: Disable global

// interrupt while erasing. Re-Enable

// GIE if needed

// Erase Flash

while(BUSY & FCTL3); // Check if Flash being used

FCTL3 = FWKEY; // Clear Lock bit

FCTL1 = FWKEY+ERASE; // Set Erase bit

*Flash_ptr = 0; // Dummy write to erase Flash seg

while(BUSY & FCTL3); // Check if Erase is done

// Write Flash

FCTL1 = FWKEY+BLKWRT+WRT; // Enable block write

for(i = 0; i < 64; i++)

{

*Flash_ptr++ = value++; // Write long int to Flash

while(!(WAIT & FCTL3)); // Test wait until ready for next byte

}

FCTL1 = FWKEY; // Clear WRT, BLKWRT

while(BUSY & FCTL3); // Check for write completion

FCTL3 = FWKEY+LOCK; // Set LOCK

}

/* Initialize non-used ISR vectors with a trap function */

/* the folowing line is the list of vectors:

#pragma vector=RTC_VECTOR

#pragma vector=PORT2_VECTOR

#pragma vector=USCI_B3_VECTOR

#pragma vector=USCI_A3_VECTOR

#pragma vector=USCI_B1_VECTOR

#pragma vector=USCI_A1_VECTOR

#pragma vector=PORT1_VECTOR

#pragma vector=TIMER1_A1_VECTOR

//#pragma vector=TIMER1_A0_VECTOR - actually used in this program

#pragma vector=DMA_VECTOR

#pragma vector=USCI_B2_VECTOR

#pragma vector=USCI_A2_VECTOR

#pragma vector=TIMER0_A1_VECTOR

#pragma vector=TIMER0_A0_VECTOR

//#pragma vector=ADC12_VECTOR - actually used in this program

#pragma vector=USCI_B0_VECTOR

#pragma vector=USCI_A0_VECTOR

#pragma vector=WDT_VECTOR

#pragma vector=TIMER0_B1_VECTOR

#pragma vector=TIMER0_B0_VECTOR

#pragma vector=UNMI_VECTOR

#pragma vector=SYSNMI_VECTOR

*/

// end of the vector list that need to be initialize.

#pragma vector= RTC_VECTOR,PORT2_VECTOR,USCI_B3_VECTOR,USCI_A3_VECTOR, \

USCI_B1_VECTOR,USCI_A1_VECTOR,PORT1_VECTOR,TIMER1_A1_VECTOR,/*TIMER1_A0_VECTOR,*/DMA_VECTOR, \

USCI_B2_VECTOR,USCI_A2_VECTOR,TIMER0_A1_VECTOR,TIMER0_A0_VECTOR, ADC12_VECTOR,\

USCI_B0_VECTOR,USCI_A0_VECTOR,WDT_VECTOR,TIMER0_B1_VECTOR,TIMER0_B0_VECTOR, \

UNMI_VECTOR,SYSNMI_VECTOR

__interrupt void ISR_trap(void)

{

// the following will cause an access violation which results in a PUC reset

WDTCTL = 0;

}

/******************************************************************************/

/* IG_lnk_msp430f5438.cmd - LINKER COMMAND FILE FOR LINKING MSP430F5438 PROGRAMS */

/* */

/* Ver | dd mmm yyyy | Who | Description of changes */

/* =====|=============|======|============================================= */

/* 0.01| 08 Mar 2004 | A.D. | First prototype */

/* 0.02| 26 Mai 2004 | A.D. | Leading symbol underscores removed, */

/* | | | Interrupt vector definition changed */

/* 0.03| 22 Jun 2004 | A.D. | File reformatted */

/* */

/* Usage: lnk430 <obj files...> -o <out file> -m <map file> lnk.cmd */

/* cl430 <src files...> -z -o <out file> -m <map file> lnk.cmd */

/* */

/*----------------------------------------------------------------------------*/

/* These linker options are for command line linking only. For IDE linking, */

/* you should set your linker options in Project Properties */

/* -c LINK USING C CONVENTIONS */

/* -stack 0x0100 SOFTWARE STACK SIZE */

/* -heap 0x0100 HEAP AREA SIZE */

/*----------------------------------------------------------------------------*/

/* 'Allocate' peripheral registers at given addresses */

/*----------------------------------------------------------------------------*/

/****************************************************************************/

MEMORY

{

SFR : origin = 0x0000, length = 0x0010

PERIPHERALS_8BIT : origin = 0x0010, length = 0x00F0

PERIPHERALS_16BIT : origin = 0x0100, length = 0x0100

RAM_MEM : origin = 0x1C00, length = 0x0200

RAM : origin = 0x1E00, length = 0x3E00

INFOA : origin = 0x1980, length = 0x0080

INFOB : origin = 0x1900, length = 0x0080

INFOC : origin = 0x1880, length = 0x0080

INFOD : origin = 0x1800, length = 0x0080

FLASH_MEM : origin = 0x5C00, length = 0x0200

FLASH_MEM_H : origin = 0x5E00, length = 0x0100

//FLASH : origin = 0x5E00, length = 0xA180

FLASH : origin = 0x5F00, length = 0xA080

FLASH2 : origin = 0x10000,length = 0x35C00

INT00 : origin = 0xFF80, length = 0x0002

INT01 : origin = 0xFF82, length = 0x0002

INT02 : origin = 0xFF84, length = 0x0002

INT03 : origin = 0xFF86, length = 0x0002

INT04 : origin = 0xFF88, length = 0x0002

INT05 : origin = 0xFF8A, length = 0x0002

INT06 : origin = 0xFF8C, length = 0x0002

INT07 : origin = 0xFF8E, length = 0x0002

INT08 : origin = 0xFF90, length = 0x0002

INT09 : origin = 0xFF92, length = 0x0002

INT10 : origin = 0xFF94, length = 0x0002

INT11 : origin = 0xFF96, length = 0x0002

INT12 : origin = 0xFF98, length = 0x0002

INT13 : origin = 0xFF9A, length = 0x0002

INT14 : origin = 0xFF9C, length = 0x0002

INT15 : origin = 0xFF9E, length = 0x0002

INT16 : origin = 0xFFA0, length = 0x0002

INT17 : origin = 0xFFA2, length = 0x0002

INT18 : origin = 0xFFA4, length = 0x0002

INT19 : origin = 0xFFA6, length = 0x0002

INT20 : origin = 0xFFA8, length = 0x0002

INT21 : origin = 0xFFAA, length = 0x0002

INT22 : origin = 0xFFAC, length = 0x0002

INT23 : origin = 0xFFAE, length = 0x0002

INT24 : origin = 0xFFB0, length = 0x0002

INT25 : origin = 0xFFB2, length = 0x0002

INT26 : origin = 0xFFB4, length = 0x0002

INT27 : origin = 0xFFB6, length = 0x0002

INT28 : origin = 0xFFB8, length = 0x0002

INT29 : origin = 0xFFBA, length = 0x0002

INT30 : origin = 0xFFBC, length = 0x0002

INT31 : origin = 0xFFBE, length = 0x0002

INT32 : origin = 0xFFC0, length = 0x0002

INT33 : origin = 0xFFC2, length = 0x0002

INT34 : origin = 0xFFC4, length = 0x0002

INT35 : origin = 0xFFC6, length = 0x0002

INT36 : origin = 0xFFC8, length = 0x0002

INT37 : origin = 0xFFCA, length = 0x0002

INT38 : origin = 0xFFCC, length = 0x0002

INT39 : origin = 0xFFCE, length = 0x0002

INT40 : origin = 0xFFD0, length = 0x0002

INT41 : origin = 0xFFD2, length = 0x0002

INT42 : origin = 0xFFD4, length = 0x0002

INT43 : origin = 0xFFD6, length = 0x0002

INT44 : origin = 0xFFD8, length = 0x0002

INT45 : origin = 0xFFDA, length = 0x0002

INT46 : origin = 0xFFDC, length = 0x0002

INT47 : origin = 0xFFDE, length = 0x0002

INT48 : origin = 0xFFE0, length = 0x0002

INT49 : origin = 0xFFE2, length = 0x0002

INT50 : origin = 0xFFE4, length = 0x0002

INT51 : origin = 0xFFE6, length = 0x0002

INT52 : origin = 0xFFE8, length = 0x0002

INT53 : origin = 0xFFEA, length = 0x0002

INT54 : origin = 0xFFEC, length = 0x0002

INT55 : origin = 0xFFEE, length = 0x0002

INT56 : origin = 0xFFF0, length = 0x0002

INT57 : origin = 0xFFF2, length = 0x0002

INT58 : origin = 0xFFF4, length = 0x0002

INT59 : origin = 0xFFF6, length = 0x0002

INT60 : origin = 0xFFF8, length = 0x0002

INT61 : origin = 0xFFFA, length = 0x0002

INT62 : origin = 0xFFFC, length = 0x0002

RESET : origin = 0xFFFE, length = 0x0002

}

/****************************************************************************/

/* SPECIFY THE SECTIONS ALLOCATION INTO MEMORY */

/****************************************************************************/

SECTIONS

{

.bss : {} > RAM /* GLOBAL & STATIC VARS */

.sysmem : {} > RAM /* DYNAMIC MEMORY ALLOCATION AREA */

.stack : {} > RAM (HIGH) /* SOFTWARE SYSTEM STACK */

.FLASHCODE : load = FLASH_MEM

run = RAM_MEM

LOAD_START(_flashcode_loadstart),

RUN_START(_flashcode_runstart),

SIZE(_flashcode_size)

/* CODE IN FLASH AND WILL BE COPIED

TO RAM AT EXECUTION HANDLED BY

USER */

.RAMCODE : load = FLASH_MEM /* CODE WILL BE IN RAM */

.text : {}>> FLASH | FLASH2 /* CODE */

.text:_isr : {} > FLASH /* ISR CODE SPACE */

.cinit : {} > FLASH /* INITIALIZATION TABLES */

.const : {} > FLASH | FLASH2 /* CONSTANT DATA */

.cio : {} > RAM /* C I/O BUFFER */

.pinit : {} > FLASH /* C++ CONSTRUCTOR TABLES */

.infoA : {} > INFOA /* MSP430 INFO FLASH MEMORY SEGMENTS */

.infoB : {} > INFOB

.infoC : {} > INFOC

.infoD : {} > INFOD

.int00 : {} > INT00 /* MSP430 INTERRUPT VECTORS */

.int01 : {} > INT01

.int02 : {} > INT02

.int03 : {} > INT03

.int04 : {} > INT04

.int05 : {} > INT05

.int06 : {} > INT06

.int07 : {} > INT07

.int08 : {} > INT08

.int09 : {} > INT09

.int10 : {} > INT10

.int11 : {} > INT11

.int12 : {} > INT12

.int13 : {} > INT13

.int14 : {} > INT14

.int15 : {} > INT15

.int16 : {} > INT16

.int17 : {} > INT17

.int18 : {} > INT18

.int19 : {} > INT19

.int20 : {} > INT20

.int21 : {} > INT21

.int22 : {} > INT22

.int23 : {} > INT23

.int24 : {} > INT24

.int25 : {} > INT25

.int26 : {} > INT26

.int27 : {} > INT27

.int28 : {} > INT28

.int29 : {} > INT29

.int30 : {} > INT30

.int31 : {} > INT31

.int32 : {} > INT32

.int33 : {} > INT33

.int34 : {} > INT34

.int35 : {} > INT35

.int36 : {} > INT36

.int37 : {} > INT37

.int38 : {} > INT38

.int39 : {} > INT39

.int40 : {} > INT40

.int41 : {} > INT41

.int42 : {} > INT42

.int43 : {} > INT43

.int44 : {} > INT44

.int45 : {} > INT45

.int46 : {} > INT46

.int47 : {} > INT47

.int48 : {} > INT48

.int49 : {} > INT49

.int50 : {} > INT50

.int51 : {} > INT51

.int52 : {} > INT52

.int53 : {} > INT53

.int54 : {} > INT54

.int55 : {} > INT55

.int56 : {} > INT56

.int57 : {} > INT57

.int58 : {} > INT58

.int59 : {} > INT59

.int60 : {} > INT60

.int61 : {} > INT61

.int62 : {} > INT62

.reset : {} > RESET /* MSP430 RESET VECTOR */

}

/****************************************************************************/

/* INCLUDE PERIPHERALS MEMORY MAP */

/****************************************************************************/

-l msp430f5438a.cmd

******************************************************************************

MSP430 Linker PC v4.1.2

******************************************************************************

>> Linked Mon Aug 25 14:22:13 2014

OUTPUT FILE NAME: <HalDev.out>

ENTRY POINT SYMBOL: "_c_int00" address: 00005f00

MEMORY CONFIGURATION

name origin length used unused attr fill

---------------------- -------- --------- -------- -------- ---- --------

SFR 00000000 00000010 00000000 00000010 RWIX

PERIPHERALS_8BIT 00000010 000000f0 00000000 000000f0 RWIX

PERIPHERALS_16BIT 00000100 00000100 00000000 00000100 RWIX

INFOD 00001800 00000080 00000000 00000080 RWIX

INFOC 00001880 00000080 00000000 00000080 RWIX

INFOB 00001900 00000080 00000000 00000080 RWIX

INFOA 00001980 00000080 00000000 00000080 RWIX

RAM_MEM 00001c00 00000200 00000098 00000168 RWIX

RAM 00001e00 00003e00 00000194 00003c6c RWIX

FLASH_MEM 00005c00 00000200 00000098 00000168 RWIX

FLASH_MEM_H 00005e00 00000100 00000000 00000100 RWIX

FLASH 00005f00 0000a080 0000051e 00009b62 RWIX

INT00 0000ff80 00000002 00000000 00000002 RWIX

INT01 0000ff82 00000002 00000000 00000002 RWIX

INT02 0000ff84 00000002 00000000 00000002 RWIX

INT03 0000ff86 00000002 00000000 00000002 RWIX

INT04 0000ff88 00000002 00000000 00000002 RWIX

INT05 0000ff8a 00000002 00000000 00000002 RWIX

INT06 0000ff8c 00000002 00000000 00000002 RWIX

INT07 0000ff8e 00000002 00000000 00000002 RWIX

INT08 0000ff90 00000002 00000000 00000002 RWIX

INT09 0000ff92 00000002 00000000 00000002 RWIX

INT10 0000ff94 00000002 00000000 00000002 RWIX

INT11 0000ff96 00000002 00000000 00000002 RWIX

INT12 0000ff98 00000002 00000000 00000002 RWIX

INT13 0000ff9a 00000002 00000000 00000002 RWIX

INT14 0000ff9c 00000002 00000000 00000002 RWIX

INT15 0000ff9e 00000002 00000000 00000002 RWIX

INT16 0000ffa0 00000002 00000000 00000002 RWIX

INT17 0000ffa2 00000002 00000000 00000002 RWIX

INT18 0000ffa4 00000002 00000000 00000002 RWIX

INT19 0000ffa6 00000002 00000000 00000002 RWIX

INT20 0000ffa8 00000002 00000000 00000002 RWIX

INT21 0000ffaa 00000002 00000000 00000002 RWIX

INT22 0000ffac 00000002 00000000 00000002 RWIX

INT23 0000ffae 00000002 00000000 00000002 RWIX

INT24 0000ffb0 00000002 00000000 00000002 RWIX

INT25 0000ffb2 00000002 00000000 00000002 RWIX

INT26 0000ffb4 00000002 00000000 00000002 RWIX

INT27 0000ffb6 00000002 00000000 00000002 RWIX

INT28 0000ffb8 00000002 00000000 00000002 RWIX

INT29 0000ffba 00000002 00000000 00000002 RWIX

INT30 0000ffbc 00000002 00000000 00000002 RWIX

INT31 0000ffbe 00000002 00000000 00000002 RWIX

INT32 0000ffc0 00000002 00000000 00000002 RWIX

INT33 0000ffc2 00000002 00000000 00000002 RWIX

INT34 0000ffc4 00000002 00000000 00000002 RWIX

INT35 0000ffc6 00000002 00000000 00000002 RWIX

INT36 0000ffc8 00000002 00000000 00000002 RWIX

INT37 0000ffca 00000002 00000000 00000002 RWIX

INT38 0000ffcc 00000002 00000000 00000002 RWIX

INT39 0000ffce 00000002 00000000 00000002 RWIX

INT40 0000ffd0 00000002 00000000 00000002 RWIX

INT41 0000ffd2 00000002 00000002 00000000 RWIX

INT42 0000ffd4 00000002 00000002 00000000 RWIX

INT43 0000ffd6 00000002 00000002 00000000 RWIX

INT44 0000ffd8 00000002 00000002 00000000 RWIX

INT45 0000ffda 00000002 00000002 00000000 RWIX

INT46 0000ffdc 00000002 00000002 00000000 RWIX

INT47 0000ffde 00000002 00000002 00000000 RWIX

INT48 0000ffe0 00000002 00000002 00000000 RWIX

INT49 0000ffe2 00000002 00000002 00000000 RWIX

INT50 0000ffe4 00000002 00000002 00000000 RWIX

INT51 0000ffe6 00000002 00000002 00000000 RWIX

INT52 0000ffe8 00000002 00000002 00000000 RWIX

INT53 0000ffea 00000002 00000002 00000000 RWIX

INT54 0000ffec 00000002 00000002 00000000 RWIX

INT55 0000ffee 00000002 00000002 00000000 RWIX

INT56 0000fff0 00000002 00000002 00000000 RWIX

INT57 0000fff2 00000002 00000002 00000000 RWIX

INT58 0000fff4 00000002 00000002 00000000 RWIX

INT59 0000fff6 00000002 00000002 00000000 RWIX

INT60 0000fff8 00000002 00000002 00000000 RWIX

INT61 0000fffa 00000002 00000002 00000000 RWIX

INT62 0000fffc 00000002 00000002 00000000 RWIX

RESET 0000fffe 00000002 00000002 00000000 RWIX

FLASH2 00010000 00035c00 00000000 00035c00 RWIX

SECTION ALLOCATION MAP

output attributes/

section page origin length input sections

-------- ---- ---------- ---------- ----------------

.bss 0 00001e00 00000004 UNINITIALIZED

00001e00 00000004 mFlash-linker.obj (.bss)

.TI.noinit

* 0 00001e00 00000000 UNINITIALIZED

.stack 0 00005a70 00000190 UNINITIALIZED

00005a70 00000004 rts430x_lc_ld_eabi.lib : boot.obj (.stack)

00005a74 0000018c --HOLE--

.FLASHCODE

* 0 00005c00 00000098 RUN ADDR = 00001c00

00005c00 00000098 mFlash-linker.obj (.FLASHCODE:write_block_int)

.text:_isr

* 0 00005f00 0000002a

00005f00 0000001a rts430x_lc_ld_eabi.lib : boot.obj (.text:_isr:_c_int00_noexit)

00005f1a 00000008 mFlash-linker.obj (.text:_isr:ISR_trap)

00005f22 00000008 Hal_Ig_Clock_Timer.obj (.text:_isr:TIMER1_A0_ISR)

.text 0 00005f2a 000004e2

00005f2a 00000108 hal_pmm.obj (.text:SetVCoreUp)

00006032 000000c8 hal_pmm.obj (.text:SetVCoreDown)

000060fa 00000096 Hal_Ig_port.obj (.text:PortCnfg)

00006190 0000007e rts430x_lc_ld_eabi.lib : autoinit.obj (.text:_auto_init)

0000620e 00000068 Hal_Ig_Clock_Timer.obj (.text:ClockCnfg)

00006276 00000050 Hal_Ig_port.obj (.text:PortDflt)

000062c6 00000042 hal_pmm.obj (.text:SetVCore)

00006308 0000003e rts430x_lc_ld_eabi.lib : asr32.obj (.text:l_asr_const)

00006346 00000030 Hal_Ig_Clock_Timer.obj (.text:TimerA1Cnfg)

00006376 0000002a rts430x_lc_ld_eabi.lib : memcpy.obj (.text:memcpy)

000063a0 00000024 : copy_zero_init.obj (.text:decompress:ZI:__TI_zero_init)

000063c4 00000024 mFlash-linker.obj (.text:main)

000063e8 00000014 mFlash-linker.obj (.text:copy_flash_to_RAM)

000063fc 0000000c system_pre_init.obj (.text:_system_pre_init)

00006408 00000004 rts430x_lc_ld_eabi.lib : exit.obj (.text:abort)

.cinit 0 0000640c 00000012

0000640c 00000006 (.cinit..bss.load) [load image, compression = zero_init]

00006412 00000004 (__TI_handler_table)

00006416 00000008 (__TI_cinit_table)

.int41 0 0000ffd2 00000002

0000ffd2 00000002 mFlash-linker.obj (.int41)

.int42 0 0000ffd4 00000002

0000ffd4 00000002 mFlash-linker.obj (.int42)

.int43 0 0000ffd6 00000002

0000ffd6 00000002 mFlash-linker.obj (.int43)

.int44 0 0000ffd8 00000002

0000ffd8 00000002 mFlash-linker.obj (.int44)

.int45 0 0000ffda 00000002

0000ffda 00000002 mFlash-linker.obj (.int45)

.int46 0 0000ffdc 00000002

0000ffdc 00000002 mFlash-linker.obj (.int46)

.int47 0 0000ffde 00000002

0000ffde 00000002 mFlash-linker.obj (.int47)

.int48 0 0000ffe0 00000002

0000ffe0 00000002 mFlash-linker.obj (.int48)

.int49 0 0000ffe2 00000002

0000ffe2 00000002 Hal_Ig_Clock_Timer.obj (.int49)

.int50 0 0000ffe4 00000002

0000ffe4 00000002 mFlash-linker.obj (.int50)

.int51 0 0000ffe6 00000002

0000ffe6 00000002 mFlash-linker.obj (.int51)

.int52 0 0000ffe8 00000002

0000ffe8 00000002 mFlash-linker.obj (.int52)

.int53 0 0000ffea 00000002

0000ffea 00000002 mFlash-linker.obj (.int53)

.int54 0 0000ffec 00000002

0000ffec 00000002 mFlash-linker.obj (.int54)

.int55 0 0000ffee 00000002

0000ffee 00000002 mFlash-linker.obj (.int55)

.int56 0 0000fff0 00000002

0000fff0 00000002 mFlash-linker.obj (.int56)

.int57 0 0000fff2 00000002

0000fff2 00000002 mFlash-linker.obj (.int57)

.int58 0 0000fff4 00000002

0000fff4 00000002 mFlash-linker.obj (.int58)

.int59 0 0000fff6 00000002

0000fff6 00000002 mFlash-linker.obj (.int59)

.int60 0 0000fff8 00000002

0000fff8 00000002 mFlash-linker.obj (.int60)

.int61 0 0000fffa 00000002

0000fffa 00000002 mFlash-linker.obj (.int61)

.int62 0 0000fffc 00000002

0000fffc 00000002 mFlash-linker.obj (.int62)

.reset 0 0000fffe 00000002

0000fffe 00000002 rts430x_lc_ld_eabi.lib : boot.obj (.reset)

LINKER GENERATED COPY TABLES

__TI_cinit_table @ 00006416 records: 1, size/record: 8, table size: 8

.bss: load addr=0000640c, load size=00000006 bytes, run addr=00001e00, run size=00000004 bytes, compression=zero_init

LINKER GENERATED HANDLER TABLE

__TI_handler_table @ 00006412 records: 1, size/record: 4, table size: 4

index: 0, handler: __TI_zero_init

GLOBAL SYMBOLS: SORTED ALPHABETICALLY BY Name

address name

-------- ----

00000700 ADC12CTL0

00000701 ADC12CTL0_H

00000700 ADC12CTL0_L

00000702 ADC12CTL1

00000703 ADC12CTL1_H

00000702 ADC12CTL1_L

00000704 ADC12CTL2

00000705 ADC12CTL2_H

00000704 ADC12CTL2_L

0000070c ADC12IE

0000070d ADC12IE_H

0000070c ADC12IE_L

0000070a ADC12IFG

0000070b ADC12IFG_H

0000070a ADC12IFG_L

0000070e ADC12IV

0000070f ADC12IV_H

0000070e ADC12IV_L

00000710 ADC12MCTL0

00000711 ADC12MCTL1

0000071a ADC12MCTL10

0000071b ADC12MCTL11

0000071c ADC12MCTL12

0000071d ADC12MCTL13

0000071e ADC12MCTL14

0000071f ADC12MCTL15

00000712 ADC12MCTL2

00000713 ADC12MCTL3

00000714 ADC12MCTL4

00000715 ADC12MCTL5

00000716 ADC12MCTL6

00000717 ADC12MCTL7

00000718 ADC12MCTL8

00000719 ADC12MCTL9

00000720 ADC12MEM0

00000721 ADC12MEM0_H

00000720 ADC12MEM0_L

00000722 ADC12MEM1

00000734 ADC12MEM10

00000735 ADC12MEM10_H

00000734 ADC12MEM10_L

00000736 ADC12MEM11

00000737 ADC12MEM11_H

00000736 ADC12MEM11_L

00000738 ADC12MEM12

00000739 ADC12MEM12_H

00000738 ADC12MEM12_L

0000073a ADC12MEM13

0000073b ADC12MEM13_H

0000073a ADC12MEM13_L

0000073c ADC12MEM14

0000073d ADC12MEM14_H

0000073c ADC12MEM14_L

0000073e ADC12MEM15

0000073f ADC12MEM15_H

0000073e ADC12MEM15_L

00000723 ADC12MEM1_H

00000722 ADC12MEM1_L

00000724 ADC12MEM2

00000725 ADC12MEM2_H

00000724 ADC12MEM2_L

00000726 ADC12MEM3

00000727 ADC12MEM3_H

00000726 ADC12MEM3_L

00000728 ADC12MEM4

00000729 ADC12MEM4_H

00000728 ADC12MEM4_L

0000072a ADC12MEM5

0000072b ADC12MEM5_H

0000072a ADC12MEM5_L

0000072c ADC12MEM6

0000072d ADC12MEM6_H

0000072c ADC12MEM6_L

0000072e ADC12MEM7

0000072f ADC12MEM7_H

0000072e ADC12MEM7_L

00000730 ADC12MEM8

00000731 ADC12MEM8_H

00000730 ADC12MEM8_L

00000732 ADC12MEM9

00000733 ADC12MEM9_H

00000732 ADC12MEM9_L

00006408 C$$EXIT

00000150 CRCDI

00000152 CRCDIRB

00000153 CRCDIRB_H

00000152 CRCDIRB_L

00000151 CRCDI_H

00000150 CRCDI_L

00000154 CRCINIRES

00000155 CRCINIRES_H

00000154 CRCINIRES_L

00000156 CRCRESR

00000157 CRCRESR_H

00000156 CRCRESR_L

0000620e ClockCnfg

00000510 DMA0CTL

00000511 DMA0CTL_H

00000510 DMA0CTL_L

00000516 DMA0DA

00000516 DMA0DAL

00000512 DMA0SA

00000512 DMA0SAL

0000051a DMA0SZ

00000520 DMA1CTL

00000521 DMA1CTL_H

00000520 DMA1CTL_L

00000526 DMA1DA

00000526 DMA1DAL

00000522 DMA1SA

00000522 DMA1SAL

0000052a DMA1SZ

00000530 DMA2CTL

00000531 DMA2CTL_H

00000530 DMA2CTL_L

00000536 DMA2DA

00000536 DMA2DAL

00000532 DMA2SA

00000532 DMA2SAL

0000053a DMA2SZ

00000500 DMACTL0

00000501 DMACTL0_H

00000500 DMACTL0_L

00000502 DMACTL1

00000503 DMACTL1_H

00000502 DMACTL1_L

00000504 DMACTL2

00000505 DMACTL2_H

00000504 DMACTL2_L

00000506 DMACTL3

00000507 DMACTL3_H

00000506 DMACTL3_L

00000508 DMACTL4

00000509 DMACTL4_H

00000508 DMACTL4_L

0000050e DMAIV

0000050f DMAIV_H

0000050e DMAIV_L

00000140 FCTL1

00000141 FCTL1_H

00000140 FCTL1_L

00000144 FCTL3

00000145 FCTL3_H

00000144 FCTL3_L

00000146 FCTL4

00000147 FCTL4_H

00000146 FCTL4_L

00005f1a ISR_trap

000004c4 MAC

000004da MAC32H

000004db MAC32H_H

000004da MAC32H_L

000004d8 MAC32L

000004d9 MAC32L_H

000004d8 MAC32L_L

000004c6 MACS

000004de MACS32H

000004df MACS32H_H

000004de MACS32H_L

000004dc MACS32L

000004dd MACS32L_H

000004dc MACS32L_L

000004c7 MACS_H

000004c6 MACS_L

000004c5 MAC_H

000004c4 MAC_L

000004c0 MPY

000004ec MPY32CTL0

000004ed MPY32CTL0_H

000004ec MPY32CTL0_L

000004d2 MPY32H

000004d3 MPY32H_H

000004d2 MPY32H_L

000004d0 MPY32L

000004d1 MPY32L_H

000004d0 MPY32L_L

000004c2 MPYS

000004d6 MPYS32H

000004d7 MPYS32H_H

000004d6 MPYS32H_L

000004d4 MPYS32L

000004d5 MPYS32L_H

000004d4 MPYS32L_L

000004c3 MPYS_H

000004c2 MPYS_L

000004c1 MPY_H

000004c0 MPY_L

000004c8 OP2

000004e2 OP2H

000004e3 OP2H_H

000004e2 OP2H_L

000004e0 OP2L

000004e1 OP2L_H

000004e0 OP2L_L

000004c9 OP2_H

000004c8 OP2_L

0000020e P1IV

0000021e P2IV

00000204 PADIR

00000205 PADIR_H

00000204 PADIR_L

00000208 PADS

00000209 PADS_H

00000208 PADS_L

0000021a PAIE

00000218 PAIES

00000219 PAIES_H

00000218 PAIES_L

0000021b PAIE_H

0000021a PAIE_L

0000021c PAIFG

0000021d PAIFG_H

0000021c PAIFG_L

00000200 PAIN

00000201 PAIN_H

00000200 PAIN_L

00000202 PAOUT

00000203 PAOUT_H

00000202 PAOUT_L

00000206 PAREN

00000207 PAREN_H

00000206 PAREN_L

0000020a PASEL

0000020b PASEL_H

0000020a PASEL_L

00000224 PBDIR

00000225 PBDIR_H

00000224 PBDIR_L

00000228 PBDS

00000229 PBDS_H

00000228 PBDS_L

00000220 PBIN

00000221 PBIN_H

00000220 PBIN_L

00000222 PBOUT

00000223 PBOUT_H

00000222 PBOUT_L

00000226 PBREN

00000227 PBREN_H

00000226 PBREN_L

0000022a PBSEL

0000022b PBSEL_H

0000022a PBSEL_L

00000244 PCDIR

00000245 PCDIR_H

00000244 PCDIR_L

00000248 PCDS

00000249 PCDS_H

00000248 PCDS_L

00000240 PCIN

00000241 PCIN_H

00000240 PCIN_L

00000242 PCOUT

00000243 PCOUT_H

00000242 PCOUT_L

00000246 PCREN

00000247 PCREN_H

00000246 PCREN_L

0000024a PCSEL

0000024b PCSEL_H

0000024a PCSEL_L

00000264 PDDIR

00000265 PDDIR_H

00000264 PDDIR_L

00000268 PDDS

00000269 PDDS_H

00000268 PDDS_L

00000260 PDIN

00000261 PDIN_H

00000260 PDIN_L

00000262 PDOUT

00000263 PDOUT_H

00000262 PDOUT_L

00000266 PDREN

00000267 PDREN_H

00000266 PDREN_L

0000026a PDSEL

0000026b PDSEL_H

0000026a PDSEL_L

00000284 PEDIR

00000285 PEDIR_H

00000284 PEDIR_L

00000288 PEDS

00000289 PEDS_H

00000288 PEDS_L

00000280 PEIN

00000281 PEIN_H

00000280 PEIN_L

00000282 PEOUT

00000283 PEOUT_H

00000282 PEOUT_L

00000286 PEREN

00000287 PEREN_H

00000286 PEREN_L

0000028a PESEL

0000028b PESEL_H

0000028a PESEL_L

000002a4 PFDIR

000002a5 PFDIR_H

000002a4 PFDIR_L

000002a8 PFDS

000002a9 PFDS_H

000002a8 PFDS_L

000002a0 PFIN

000002a1 PFIN_H

000002a0 PFIN_L

000002a2 PFOUT

000002a3 PFOUT_H

000002a2 PFOUT_L

000002a6 PFREN

000002a7 PFREN_H

000002a6 PFREN_L

000002aa PFSEL

000002ab PFSEL_H

000002aa PFSEL_L

00000324 PJDIR

00000325 PJDIR_H

00000324 PJDIR_L

00000328 PJDS

00000329 PJDS_H

00000328 PJDS_L

00000320 PJIN

00000321 PJIN_H

00000320 PJIN_L

00000322 PJOUT

00000323 PJOUT_H

00000322 PJOUT_L

00000326 PJREN

00000327 PJREN_H

00000326 PJREN_L

00000130 PM5CTL0

00000131 PM5CTL0_H

00000130 PM5CTL0_L

00000120 PMMCTL0

00000121 PMMCTL0_H

00000120 PMMCTL0_L

00000122 PMMCTL1

00000123 PMMCTL1_H

00000122 PMMCTL1_L

0000012c PMMIFG

0000012d PMMIFG_H

0000012c PMMIFG_L

0000012e PMMRIE

0000012f PMMRIE_H

0000012e PMMRIE_L

000060fa PortCnfg

00000158 RCCTL0

00000159 RCCTL0_H

00000158 RCCTL0_L

000001b0 REFCTL0

000001b1 REFCTL0_H

000001b0 REFCTL0_L

000004e4 RES0

000004e5 RES0_H

000004e4 RES0_L

000004e6 RES1

000004e7 RES1_H

000004e6 RES1_L

000004e8 RES2

000004e9 RES2_H

000004e8 RES2_L

000004ea RES3

000004eb RES3_H

000004ea RES3_L

000004cc RESHI

000004cd RESHI_H

000004cc RESHI_L

000004ca RESLO

000004cb RESLO_H

000004ca RESLO_L

000004ba RTCADOWDAY

000004bb RTCADOWDAY_H

000004ba RTCADOWDAY_L

000004b8 RTCAMINHR

000004b9 RTCAMINHR_H

000004b8 RTCAMINHR_L

000004a0 RTCCTL01

000004a1 RTCCTL01_H

000004a0 RTCCTL01_L

000004a2 RTCCTL23

000004a3 RTCCTL23_H

000004a2 RTCCTL23_L

000004b4 RTCDATE

000004b5 RTCDATE_H

000004b4 RTCDATE_L

000004ae RTCIV

000004ac RTCPS

000004a8 RTCPS0CTL

000004a9 RTCPS0CTL_H

000004a8 RTCPS0CTL_L

000004aa RTCPS1CTL

000004ab RTCPS1CTL_H

000004aa RTCPS1CTL_L

000004ad RTCPS_H

000004ac RTCPS_L

000004b0 RTCTIM0

000004b1 RTCTIM0_H

000004b0 RTCTIM0_L

000004b2 RTCTIM1

000004b3 RTCTIM1_H

000004b2 RTCTIM1_L

000004b6 RTCYEAR

000004b7 RTCYEAR_H

000004b6 RTCYEAR_L

00000100 SFRIE1

00000101 SFRIE1_H

00000100 SFRIE1_L

00000102 SFRIFG1

00000103 SFRIFG1_H

00000102 SFRIFG1_L

00000104 SFRRPCR

00000105 SFRRPCR_H

00000104 SFRRPCR_L

000004ce SUMEXT

000004cf SUMEXT_H

000004ce SUMEXT_L

00000124 SVSMHCTL

00000125 SVSMHCTL_H

00000124 SVSMHCTL_L

00000128 SVSMIO

00000129 SVSMIO_H

00000128 SVSMIO_L

00000126 SVSMLCTL

00000127 SVSMLCTL_H

00000126 SVSMLCTL_L

00000198 SYSBERRIV

00000199 SYSBERRIV_H

00000198 SYSBERRIV_L

00000182 SYSBSLC

00000183 SYSBSLC_H

00000182 SYSBSLC_L

00000180 SYSCTL

00000181 SYSCTL_H

00000180 SYSCTL_L

00000186 SYSJMBC

00000187 SYSJMBC_H

00000186 SYSJMBC_L

00000188 SYSJMBI0

00000189 SYSJMBI0_H

00000188 SYSJMBI0_L

0000018a SYSJMBI1

0000018b SYSJMBI1_H

0000018a SYSJMBI1_L

0000018c SYSJMBO0

0000018d SYSJMBO0_H

0000018c SYSJMBO0_L

0000018e SYSJMBO1

0000018f SYSJMBO1_H

0000018e SYSJMBO1_L

0000019e SYSRSTIV

0000019f SYSRSTIV_H

0000019e SYSRSTIV_L

0000019c SYSSNIV

0000019d SYSSNIV_H

0000019c SYSSNIV_L

0000019a SYSUNIV

0000019b SYSUNIV_H

0000019a SYSUNIV_L

000062c6 SetVCore

00006032 SetVCoreDown

00005f2a SetVCoreUp

00000352 TA0CCR0

00000354 TA0CCR1

00000356 TA0CCR2

00000358 TA0CCR3

0000035a TA0CCR4

00000342 TA0CCTL0

00000344 TA0CCTL1

00000346 TA0CCTL2

00000348 TA0CCTL3

0000034a TA0CCTL4

00000340 TA0CTL

00000360 TA0EX0

0000036e TA0IV

00000350 TA0R

00000392 TA1CCR0

00000394 TA1CCR1

00000396 TA1CCR2

00000382 TA1CCTL0

00000384 TA1CCTL1

00000386 TA1CCTL2

00000380 TA1CTL

000003a0 TA1EX0

000003ae TA1IV

00000390 TA1R

000003d2 TB0CCR0

000003d4 TB0CCR1

000003d6 TB0CCR2

000003d8 TB0CCR3

000003da TB0CCR4

000003dc TB0CCR5

000003de TB0CCR6

000003c2 TB0CCTL0

000003c4 TB0CCTL1

000003c6 TB0CCTL2

000003c8 TB0CCTL3

000003ca TB0CCTL4

000003cc TB0CCTL5

000003ce TB0CCTL6

000003c0 TB0CTL

000003e0 TB0EX0

000003ee TB0IV

000003d0 TB0R

00005f22 TIMER1_A0_ISR

00006346 TimerA1Cnfg

000005d0 UCA0ABCTL

000005c6 UCA0BRW

000005c7 UCA0BRW_H

000005c6 UCA0BRW_L

000005c0 UCA0CTLW0

000005c1 UCA0CTLW0_H

000005c0 UCA0CTLW0_L

000005dc UCA0ICTL

000005dd UCA0ICTL_H

000005dc UCA0ICTL_L

000005d2 UCA0IRCTL

000005d3 UCA0IRCTL_H

000005d2 UCA0IRCTL_L

000005de UCA0IV

000005c8 UCA0MCTL

000005cc UCA0RXBUF

000005ca UCA0STAT

000005ce UCA0TXBUF

00000610 UCA1ABCTL

00000606 UCA1BRW

00000607 UCA1BRW_H

00000606 UCA1BRW_L

00000600 UCA1CTLW0

00000601 UCA1CTLW0_H

00000600 UCA1CTLW0_L

0000061c UCA1ICTL

0000061d UCA1ICTL_H

0000061c UCA1ICTL_L

00000612 UCA1IRCTL

00000613 UCA1IRCTL_H

00000612 UCA1IRCTL_L

0000061e UCA1IV

00000608 UCA1MCTL

0000060c UCA1RXBUF

0000060a UCA1STAT

0000060e UCA1TXBUF

00000650 UCA2ABCTL

00000646 UCA2BRW

00000647 UCA2BRW_H

00000646 UCA2BRW_L

00000640 UCA2CTLW0

00000641 UCA2CTLW0_H

00000640 UCA2CTLW0_L

0000065c UCA2ICTL

0000065d UCA2ICTL_H

0000065c UCA2ICTL_L

00000652 UCA2IRCTL

00000653 UCA2IRCTL_H

00000652 UCA2IRCTL_L

0000065e UCA2IV

00000648 UCA2MCTL

0000064c UCA2RXBUF

0000064a UCA2STAT

0000064e UCA2TXBUF

00000690 UCA3ABCTL

00000686 UCA3BRW

00000687 UCA3BRW_H

00000686 UCA3BRW_L

00000680 UCA3CTLW0

00000681 UCA3CTLW0_H

00000680 UCA3CTLW0_L

0000069c UCA3ICTL

0000069d UCA3ICTL_H

0000069c UCA3ICTL_L

00000692 UCA3IRCTL

00000693 UCA3IRCTL_H

00000692 UCA3IRCTL_L

0000069e UCA3IV

00000688 UCA3MCTL

0000068c UCA3RXBUF

0000068a UCA3STAT

0000068e UCA3TXBUF

000005e6 UCB0BRW

000005e7 UCB0BRW_H

000005e6 UCB0BRW_L

000005e0 UCB0CTLW0

000005e1 UCB0CTLW0_H

000005e0 UCB0CTLW0_L

000005f0 UCB0I2COA

000005f1 UCB0I2COA_H

000005f0 UCB0I2COA_L

000005f2 UCB0I2CSA

000005f3 UCB0I2CSA_H

000005f2 UCB0I2CSA_L

000005fc UCB0ICTL

000005fd UCB0ICTL_H

000005fc UCB0ICTL_L

000005fe UCB0IV

000005ec UCB0RXBUF

000005ea UCB0STAT

000005ee UCB0TXBUF

00000626 UCB1BRW

00000627 UCB1BRW_H

00000626 UCB1BRW_L

00000620 UCB1CTLW0

00000621 UCB1CTLW0_H

00000620 UCB1CTLW0_L

00000630 UCB1I2COA

00000631 UCB1I2COA_H

00000630 UCB1I2COA_L

00000632 UCB1I2CSA

00000633 UCB1I2CSA_H

00000632 UCB1I2CSA_L

0000063c UCB1ICTL

0000063d UCB1ICTL_H

0000063c UCB1ICTL_L

0000063e UCB1IV

0000062c UCB1RXBUF

0000062a UCB1STAT

0000062e UCB1TXBUF

00000666 UCB2BRW

00000667 UCB2BRW_H

00000666 UCB2BRW_L

00000660 UCB2CTLW0

00000661 UCB2CTLW0_H

00000660 UCB2CTLW0_L

00000670 UCB2I2COA

00000671 UCB2I2COA_H

00000670 UCB2I2COA_L

00000672 UCB2I2CSA

00000673 UCB2I2CSA_H

00000672 UCB2I2CSA_L

0000067c UCB2ICTL

0000067d UCB2ICTL_H

0000067c UCB2ICTL_L

0000067e UCB2IV

0000066c UCB2RXBUF

0000066a UCB2STAT

0000066e UCB2TXBUF

000006a6 UCB3BRW

000006a7 UCB3BRW_H

000006a6 UCB3BRW_L

000006a0 UCB3CTLW0

000006a1 UCB3CTLW0_H

000006a0 UCB3CTLW0_L

000006b0 UCB3I2COA

000006b1 UCB3I2COA_H

000006b0 UCB3I2COA_L

000006b2 UCB3I2CSA

000006b3 UCB3I2CSA_H

000006b2 UCB3I2CSA_L

000006bc UCB3ICTL

000006bd UCB3ICTL_H

000006bc UCB3ICTL_L

000006be UCB3IV

000006ac UCB3RXBUF

000006aa UCB3STAT

000006ae UCB3TXBUF

00000160 UCSCTL0

00000161 UCSCTL0_H

00000160 UCSCTL0_L

00000162 UCSCTL1

00000163 UCSCTL1_H

00000162 UCSCTL1_L

00000164 UCSCTL2

00000165 UCSCTL2_H

00000164 UCSCTL2_L

00000166 UCSCTL3

00000167 UCSCTL3_H

00000166 UCSCTL3_L

00000168 UCSCTL4

00000169 UCSCTL4_H

00000168 UCSCTL4_L

0000016a UCSCTL5

0000016b UCSCTL5_H

0000016a UCSCTL5_L

0000016c UCSCTL6

0000016d UCSCTL6_H

0000016c UCSCTL6_L

0000016e UCSCTL7

0000016f UCSCTL7_H

0000016e UCSCTL7_L

00000170 UCSCTL8

00000171 UCSCTL8_H

00000170 UCSCTL8_L

0000015c WDTCTL

0000015d WDTCTL_H

0000015c WDTCTL_L

00005c00 __STACK_END

00000190 __STACK_SIZE

00006416 __TI_CINIT_Base

0000641e __TI_CINIT_Limit

00006412 __TI_Handler_Table_Base

00006416 __TI_Handler_Table_Limit

UNDEFED __TI_INITARRAY_Base

UNDEFED __TI_INITARRAY_Limit

00000001 __TI_args_main

00000001 __TI_exit

000063a0 __TI_zero_init

ffffffff __binit__

ffffffff __c_args__

00006340 __mspabi_sral_1

0000631c __mspabi_sral_10

00006318 __mspabi_sral_11

00006314 __mspabi_sral_12

00006310 __mspabi_sral_13

0000630c __mspabi_sral_14

00006308 __mspabi_sral_15

0000633c __mspabi_sral_2

00006338 __mspabi_sral_3

00006334 __mspabi_sral_4

00006330 __mspabi_sral_5

0000632c __mspabi_sral_6

00006328 __mspabi_sral_7

00006324 __mspabi_sral_8

00006320 __mspabi_sral_9

00006190 _auto_init

00005f00 _c_int00

00005f00 _c_int00_noexit

00005c00 _flashcode_loadstart

00001c00 _flashcode_runstart

00000098 _flashcode_size

0000fffe _reset_vector

00005a70 _stack

000063fc _system_pre_init

00006408 abort

ffffffff binit

000063e8 copy_flash_to_RAM

000063c4 main

00006376 memcpy

00001e00 value

00001c00 write_block_int

GLOBAL SYMBOLS: SORTED BY Symbol Address

address name

-------- ----

00000001 __TI_args_main

00000001 __TI_exit

00000098 _flashcode_size

00000100 SFRIE1

00000100 SFRIE1_L

00000101 SFRIE1_H

00000102 SFRIFG1

00000102 SFRIFG1_L

00000103 SFRIFG1_H

00000104 SFRRPCR

00000104 SFRRPCR_L

00000105 SFRRPCR_H

00000120 PMMCTL0

00000120 PMMCTL0_L

00000121 PMMCTL0_H

00000122 PMMCTL1

00000122 PMMCTL1_L

00000123 PMMCTL1_H

00000124 SVSMHCTL

00000124 SVSMHCTL_L

00000125 SVSMHCTL_H

00000126 SVSMLCTL

00000126 SVSMLCTL_L

00000127 SVSMLCTL_H

00000128 SVSMIO

00000128 SVSMIO_L

00000129 SVSMIO_H

0000012c PMMIFG

0000012c PMMIFG_L

0000012d PMMIFG_H

0000012e PMMRIE

0000012e PMMRIE_L

0000012f PMMRIE_H

00000130 PM5CTL0

00000130 PM5CTL0_L

00000131 PM5CTL0_H

00000140 FCTL1

00000140 FCTL1_L

00000141 FCTL1_H

00000144 FCTL3

00000144 FCTL3_L

00000145 FCTL3_H

00000146 FCTL4

00000146 FCTL4_L

00000147 FCTL4_H

00000150 CRCDI

00000150 CRCDI_L

00000151 CRCDI_H

00000152 CRCDIRB

00000152 CRCDIRB_L

00000153 CRCDIRB_H

00000154 CRCINIRES

00000154 CRCINIRES_L

00000155 CRCINIRES_H

00000156 CRCRESR

00000156 CRCRESR_L

00000157 CRCRESR_H

00000158 RCCTL0

00000158 RCCTL0_L

00000159 RCCTL0_H

0000015c WDTCTL

0000015c WDTCTL_L

0000015d WDTCTL_H

00000160 UCSCTL0

00000160 UCSCTL0_L

00000161 UCSCTL0_H

00000162 UCSCTL1

00000162 UCSCTL1_L

00000163 UCSCTL1_H

00000164 UCSCTL2

00000164 UCSCTL2_L

00000165 UCSCTL2_H

00000166 UCSCTL3

00000166 UCSCTL3_L

00000167 UCSCTL3_H

00000168 UCSCTL4

00000168 UCSCTL4_L

00000169 UCSCTL4_H

0000016a UCSCTL5

0000016a UCSCTL5_L

0000016b UCSCTL5_H

0000016c UCSCTL6

0000016c UCSCTL6_L

0000016d UCSCTL6_H

0000016e UCSCTL7

0000016e UCSCTL7_L

0000016f UCSCTL7_H

00000170 UCSCTL8

00000170 UCSCTL8_L

00000171 UCSCTL8_H

00000180 SYSCTL

00000180 SYSCTL_L

00000181 SYSCTL_H

00000182 SYSBSLC

00000182 SYSBSLC_L

00000183 SYSBSLC_H

00000186 SYSJMBC

00000186 SYSJMBC_L

00000187 SYSJMBC_H

00000188 SYSJMBI0

00000188 SYSJMBI0_L

00000189 SYSJMBI0_H

0000018a SYSJMBI1

0000018a SYSJMBI1_L

0000018b SYSJMBI1_H

0000018c SYSJMBO0

0000018c SYSJMBO0_L

0000018d SYSJMBO0_H

0000018e SYSJMBO1

0000018e SYSJMBO1_L

0000018f SYSJMBO1_H

00000190 __STACK_SIZE

00000198 SYSBERRIV

00000198 SYSBERRIV_L

00000199 SYSBERRIV_H

0000019a SYSUNIV

0000019a SYSUNIV_L

0000019b SYSUNIV_H

0000019c SYSSNIV

0000019c SYSSNIV_L

0000019d SYSSNIV_H

0000019e SYSRSTIV

0000019e SYSRSTIV_L

0000019f SYSRSTIV_H

000001b0 REFCTL0

000001b0 REFCTL0_L

000001b1 REFCTL0_H

00000200 PAIN

00000200 PAIN_L

00000201 PAIN_H

00000202 PAOUT

00000202 PAOUT_L

00000203 PAOUT_H

00000204 PADIR

00000204 PADIR_L

00000205 PADIR_H

00000206 PAREN

00000206 PAREN_L

00000207 PAREN_H

00000208 PADS

00000208 PADS_L

00000209 PADS_H

0000020a PASEL

0000020a PASEL_L

0000020b PASEL_H

0000020e P1IV

00000218 PAIES

00000218 PAIES_L

00000219 PAIES_H

0000021a PAIE

0000021a PAIE_L

0000021b PAIE_H

0000021c PAIFG

0000021c PAIFG_L

0000021d PAIFG_H

0000021e P2IV

00000220 PBIN

00000220 PBIN_L

00000221 PBIN_H

00000222 PBOUT

00000222 PBOUT_L

00000223 PBOUT_H

00000224 PBDIR

00000224 PBDIR_L

00000225 PBDIR_H

00000226 PBREN

00000226 PBREN_L

00000227 PBREN_H

00000228 PBDS

00000228 PBDS_L

00000229 PBDS_H

0000022a PBSEL

0000022a PBSEL_L

0000022b PBSEL_H

00000240 PCIN

00000240 PCIN_L

00000241 PCIN_H

00000242 PCOUT

00000242 PCOUT_L

00000243 PCOUT_H

00000244 PCDIR

00000244 PCDIR_L

00000245 PCDIR_H

00000246 PCREN

00000246 PCREN_L

00000247 PCREN_H

00000248 PCDS

00000248 PCDS_L

00000249 PCDS_H

0000024a PCSEL

0000024a PCSEL_L

0000024b PCSEL_H

00000260 PDIN

00000260 PDIN_L

00000261 PDIN_H

00000262 PDOUT

00000262 PDOUT_L

00000263 PDOUT_H

00000264 PDDIR

00000264 PDDIR_L

00000265 PDDIR_H

00000266 PDREN

00000266 PDREN_L

00000267 PDREN_H

00000268 PDDS

00000268 PDDS_L

00000269 PDDS_H

0000026a PDSEL

0000026a PDSEL_L

0000026b PDSEL_H

00000280 PEIN

00000280 PEIN_L

00000281 PEIN_H

00000282 PEOUT

00000282 PEOUT_L

00000283 PEOUT_H

00000284 PEDIR

00000284 PEDIR_L

00000285 PEDIR_H

00000286 PEREN

00000286 PEREN_L

00000287 PEREN_H

00000288 PEDS

00000288 PEDS_L

00000289 PEDS_H

0000028a PESEL

0000028a PESEL_L

0000028b PESEL_H

000002a0 PFIN

000002a0 PFIN_L

000002a1 PFIN_H

000002a2 PFOUT

000002a2 PFOUT_L

000002a3 PFOUT_H

000002a4 PFDIR

000002a4 PFDIR_L

000002a5 PFDIR_H

000002a6 PFREN

000002a6 PFREN_L

000002a7 PFREN_H

000002a8 PFDS

000002a8 PFDS_L

000002a9 PFDS_H

000002aa PFSEL

000002aa PFSEL_L

000002ab PFSEL_H

00000320 PJIN

00000320 PJIN_L

00000321 PJIN_H

00000322 PJOUT

00000322 PJOUT_L

00000323 PJOUT_H

00000324 PJDIR

00000324 PJDIR_L

00000325 PJDIR_H

00000326 PJREN

00000326 PJREN_L

00000327 PJREN_H

00000328 PJDS

00000328 PJDS_L

00000329 PJDS_H

00000340 TA0CTL

00000342 TA0CCTL0

00000344 TA0CCTL1

00000346 TA0CCTL2

00000348 TA0CCTL3

0000034a TA0CCTL4

00000350 TA0R

00000352 TA0CCR0

00000354 TA0CCR1

00000356 TA0CCR2

00000358 TA0CCR3

0000035a TA0CCR4

00000360 TA0EX0

0000036e TA0IV

00000380 TA1CTL

00000382 TA1CCTL0

00000384 TA1CCTL1

00000386 TA1CCTL2

00000390 TA1R

00000392 TA1CCR0

00000394 TA1CCR1

00000396 TA1CCR2

000003a0 TA1EX0

000003ae TA1IV

000003c0 TB0CTL

000003c2 TB0CCTL0

000003c4 TB0CCTL1

000003c6 TB0CCTL2

000003c8 TB0CCTL3

000003ca TB0CCTL4

000003cc TB0CCTL5

000003ce TB0CCTL6

000003d0 TB0R

000003d2 TB0CCR0

000003d4 TB0CCR1

000003d6 TB0CCR2

000003d8 TB0CCR3

000003da TB0CCR4

000003dc TB0CCR5

000003de TB0CCR6

000003e0 TB0EX0

000003ee TB0IV

000004a0 RTCCTL01

000004a0 RTCCTL01_L

000004a1 RTCCTL01_H

000004a2 RTCCTL23

000004a2 RTCCTL23_L

000004a3 RTCCTL23_H

000004a8 RTCPS0CTL

000004a8 RTCPS0CTL_L

000004a9 RTCPS0CTL_H

000004aa RTCPS1CTL

000004aa RTCPS1CTL_L

000004ab RTCPS1CTL_H

000004ac RTCPS

000004ac RTCPS_L

000004ad RTCPS_H

000004ae RTCIV

000004b0 RTCTIM0

000004b0 RTCTIM0_L

000004b1 RTCTIM0_H

000004b2 RTCTIM1

000004b2 RTCTIM1_L

000004b3 RTCTIM1_H

000004b4 RTCDATE

000004b4 RTCDATE_L

000004b5 RTCDATE_H

000004b6 RTCYEAR

000004b6 RTCYEAR_L

000004b7 RTCYEAR_H

000004b8 RTCAMINHR

000004b8 RTCAMINHR_L

000004b9 RTCAMINHR_H

000004ba RTCADOWDAY

000004ba RTCADOWDAY_L

000004bb RTCADOWDAY_H

000004c0 MPY

000004c0 MPY_L

000004c1 MPY_H

000004c2 MPYS

000004c2 MPYS_L

000004c3 MPYS_H

000004c4 MAC

000004c4 MAC_L

000004c5 MAC_H

000004c6 MACS

000004c6 MACS_L

000004c7 MACS_H

000004c8 OP2

000004c8 OP2_L

000004c9 OP2_H

000004ca RESLO

000004ca RESLO_L

000004cb RESLO_H

000004cc RESHI

000004cc RESHI_L

000004cd RESHI_H

000004ce SUMEXT

000004ce SUMEXT_L

000004cf SUMEXT_H

000004d0 MPY32L

000004d0 MPY32L_L

000004d1 MPY32L_H

000004d2 MPY32H

000004d2 MPY32H_L

000004d3 MPY32H_H

000004d4 MPYS32L

000004d4 MPYS32L_L

000004d5 MPYS32L_H

000004d6 MPYS32H

000004d6 MPYS32H_L

000004d7 MPYS32H_H

000004d8 MAC32L

000004d8 MAC32L_L

000004d9 MAC32L_H

000004da MAC32H

000004da MAC32H_L

000004db MAC32H_H

000004dc MACS32L

000004dc MACS32L_L

000004dd MACS32L_H

000004de MACS32H

000004de MACS32H_L

000004df MACS32H_H

000004e0 OP2L

000004e0 OP2L_L

000004e1 OP2L_H

000004e2 OP2H

000004e2 OP2H_L

000004e3 OP2H_H

000004e4 RES0

000004e4 RES0_L

000004e5 RES0_H

000004e6 RES1

000004e6 RES1_L

000004e7 RES1_H

000004e8 RES2

000004e8 RES2_L

000004e9 RES2_H

000004ea RES3

000004ea RES3_L

000004eb RES3_H

000004ec MPY32CTL0

000004ec MPY32CTL0_L

000004ed MPY32CTL0_H

00000500 DMACTL0

00000500 DMACTL0_L

00000501 DMACTL0_H

00000502 DMACTL1

00000502 DMACTL1_L

00000503 DMACTL1_H

00000504 DMACTL2

00000504 DMACTL2_L

00000505 DMACTL2_H

00000506 DMACTL3

00000506 DMACTL3_L

00000507 DMACTL3_H

00000508 DMACTL4

00000508 DMACTL4_L

00000509 DMACTL4_H

0000050e DMAIV

0000050e DMAIV_L

0000050f DMAIV_H

00000510 DMA0CTL

00000510 DMA0CTL_L

00000511 DMA0CTL_H

00000512 DMA0SA

00000512 DMA0SAL

00000516 DMA0DA

00000516 DMA0DAL

0000051a DMA0SZ

00000520 DMA1CTL

00000520 DMA1CTL_L

00000521 DMA1CTL_H

00000522 DMA1SA

00000522 DMA1SAL

00000526 DMA1DA

00000526 DMA1DAL

0000052a DMA1SZ

00000530 DMA2CTL

00000530 DMA2CTL_L

00000531 DMA2CTL_H

00000532 DMA2SA

00000532 DMA2SAL

00000536 DMA2DA

00000536 DMA2DAL

0000053a DMA2SZ

000005c0 UCA0CTLW0

000005c0 UCA0CTLW0_L

000005c1 UCA0CTLW0_H

000005c6 UCA0BRW

000005c6 UCA0BRW_L

000005c7 UCA0BRW_H

000005c8 UCA0MCTL

000005ca UCA0STAT

000005cc UCA0RXBUF

000005ce UCA0TXBUF

000005d0 UCA0ABCTL

000005d2 UCA0IRCTL

000005d2 UCA0IRCTL_L

000005d3 UCA0IRCTL_H

000005dc UCA0ICTL

000005dc UCA0ICTL_L

000005dd UCA0ICTL_H

000005de UCA0IV

000005e0 UCB0CTLW0

000005e0 UCB0CTLW0_L

000005e1 UCB0CTLW0_H

000005e6 UCB0BRW

000005e6 UCB0BRW_L

000005e7 UCB0BRW_H

000005ea UCB0STAT

000005ec UCB0RXBUF

000005ee UCB0TXBUF

000005f0 UCB0I2COA

000005f0 UCB0I2COA_L

000005f1 UCB0I2COA_H

000005f2 UCB0I2CSA

000005f2 UCB0I2CSA_L

000005f3 UCB0I2CSA_H

000005fc UCB0ICTL

000005fc UCB0ICTL_L

000005fd UCB0ICTL_H

000005fe UCB0IV

00000600 UCA1CTLW0

00000600 UCA1CTLW0_L

00000601 UCA1CTLW0_H

00000606 UCA1BRW

00000606 UCA1BRW_L

00000607 UCA1BRW_H

00000608 UCA1MCTL

0000060a UCA1STAT

0000060c UCA1RXBUF

0000060e UCA1TXBUF

00000610 UCA1ABCTL

00000612 UCA1IRCTL

00000612 UCA1IRCTL_L

00000613 UCA1IRCTL_H

0000061c UCA1ICTL

0000061c UCA1ICTL_L

0000061d UCA1ICTL_H

0000061e UCA1IV

00000620 UCB1CTLW0

00000620 UCB1CTLW0_L

00000621 UCB1CTLW0_H

00000626 UCB1BRW

00000626 UCB1BRW_L

00000627 UCB1BRW_H

0000062a UCB1STAT

0000062c UCB1RXBUF

0000062e UCB1TXBUF

00000630 UCB1I2COA

00000630 UCB1I2COA_L

00000631 UCB1I2COA_H

00000632 UCB1I2CSA

00000632 UCB1I2CSA_L

00000633 UCB1I2CSA_H

0000063c UCB1ICTL

0000063c UCB1ICTL_L

0000063d UCB1ICTL_H

0000063e UCB1IV

00000640 UCA2CTLW0

00000640 UCA2CTLW0_L

00000641 UCA2CTLW0_H

00000646 UCA2BRW

00000646 UCA2BRW_L

00000647 UCA2BRW_H

00000648 UCA2MCTL

0000064a UCA2STAT

0000064c UCA2RXBUF

0000064e UCA2TXBUF

00000650 UCA2ABCTL

00000652 UCA2IRCTL

00000652 UCA2IRCTL_L

00000653 UCA2IRCTL_H

0000065c UCA2ICTL

0000065c UCA2ICTL_L

0000065d UCA2ICTL_H

0000065e UCA2IV

00000660 UCB2CTLW0

00000660 UCB2CTLW0_L

00000661 UCB2CTLW0_H

00000666 UCB2BRW

00000666 UCB2BRW_L

00000667 UCB2BRW_H

0000066a UCB2STAT

0000066c UCB2RXBUF

0000066e UCB2TXBUF

00000670 UCB2I2COA

00000670 UCB2I2COA_L

00000671 UCB2I2COA_H

00000672 UCB2I2CSA

00000672 UCB2I2CSA_L

00000673 UCB2I2CSA_H

0000067c UCB2ICTL

0000067c UCB2ICTL_L

0000067d UCB2ICTL_H

0000067e UCB2IV

00000680 UCA3CTLW0

00000680 UCA3CTLW0_L

00000681 UCA3CTLW0_H

00000686 UCA3BRW

00000686 UCA3BRW_L

00000687 UCA3BRW_H

00000688 UCA3MCTL

0000068a UCA3STAT

0000068c UCA3RXBUF

0000068e UCA3TXBUF

00000690 UCA3ABCTL

00000692 UCA3IRCTL

00000692 UCA3IRCTL_L

00000693 UCA3IRCTL_H

0000069c UCA3ICTL

0000069c UCA3ICTL_L

0000069d UCA3ICTL_H

0000069e UCA3IV

000006a0 UCB3CTLW0

000006a0 UCB3CTLW0_L

000006a1 UCB3CTLW0_H

000006a6 UCB3BRW

000006a6 UCB3BRW_L

000006a7 UCB3BRW_H

000006aa UCB3STAT

000006ac UCB3RXBUF

000006ae UCB3TXBUF

000006b0 UCB3I2COA

000006b0 UCB3I2COA_L

000006b1 UCB3I2COA_H

000006b2 UCB3I2CSA

000006b2 UCB3I2CSA_L

000006b3 UCB3I2CSA_H

000006bc UCB3ICTL

000006bc UCB3ICTL_L

000006bd UCB3ICTL_H

000006be UCB3IV

00000700 ADC12CTL0

00000700 ADC12CTL0_L

00000701 ADC12CTL0_H

00000702 ADC12CTL1

00000702 ADC12CTL1_L

00000703 ADC12CTL1_H

00000704 ADC12CTL2

00000704 ADC12CTL2_L

00000705 ADC12CTL2_H

0000070a ADC12IFG

0000070a ADC12IFG_L

0000070b ADC12IFG_H

0000070c ADC12IE

0000070c ADC12IE_L

0000070d ADC12IE_H

0000070e ADC12IV

0000070e ADC12IV_L

0000070f ADC12IV_H

00000710 ADC12MCTL0

00000711 ADC12MCTL1

00000712 ADC12MCTL2

00000713 ADC12MCTL3

00000714 ADC12MCTL4

00000715 ADC12MCTL5

00000716 ADC12MCTL6

00000717 ADC12MCTL7

00000718 ADC12MCTL8

00000719 ADC12MCTL9

0000071a ADC12MCTL10

0000071b ADC12MCTL11

0000071c ADC12MCTL12

0000071d ADC12MCTL13

0000071e ADC12MCTL14

0000071f ADC12MCTL15

00000720 ADC12MEM0

00000720 ADC12MEM0_L

00000721 ADC12MEM0_H

00000722 ADC12MEM1

00000722 ADC12MEM1_L

00000723 ADC12MEM1_H

00000724 ADC12MEM2

00000724 ADC12MEM2_L

00000725 ADC12MEM2_H

00000726 ADC12MEM3

00000726 ADC12MEM3_L

00000727 ADC12MEM3_H

00000728 ADC12MEM4

00000728 ADC12MEM4_L

00000729 ADC12MEM4_H

0000072a ADC12MEM5

0000072a ADC12MEM5_L

0000072b ADC12MEM5_H

0000072c ADC12MEM6

0000072c ADC12MEM6_L

0000072d ADC12MEM6_H

0000072e ADC12MEM7

0000072e ADC12MEM7_L

0000072f ADC12MEM7_H

00000730 ADC12MEM8

00000730 ADC12MEM8_L

00000731 ADC12MEM8_H

00000732 ADC12MEM9

00000732 ADC12MEM9_L

00000733 ADC12MEM9_H

00000734 ADC12MEM10

00000734 ADC12MEM10_L

00000735 ADC12MEM10_H

00000736 ADC12MEM11

00000736 ADC12MEM11_L

00000737 ADC12MEM11_H

00000738 ADC12MEM12

00000738 ADC12MEM12_L

00000739 ADC12MEM12_H

0000073a ADC12MEM13

0000073a ADC12MEM13_L

0000073b ADC12MEM13_H

0000073c ADC12MEM14

0000073c ADC12MEM14_L

0000073d ADC12MEM14_H

0000073e ADC12MEM15

0000073e ADC12MEM15_L

0000073f ADC12MEM15_H

00001c00 _flashcode_runstart

00001c00 write_block_int

00001e00 value

00005a70 _stack

00005c00 __STACK_END

00005c00 _flashcode_loadstart

00005f00 _c_int00

00005f00 _c_int00_noexit

00005f1a ISR_trap

00005f22 TIMER1_A0_ISR

00005f2a SetVCoreUp

00006032 SetVCoreDown

000060fa PortCnfg

00006190 _auto_init

0000620e ClockCnfg

000062c6 SetVCore

00006308 __mspabi_sral_15

0000630c __mspabi_sral_14

00006310 __mspabi_sral_13

00006314 __mspabi_sral_12

00006318 __mspabi_sral_11

0000631c __mspabi_sral_10

00006320 __mspabi_sral_9

00006324 __mspabi_sral_8

00006328 __mspabi_sral_7

0000632c __mspabi_sral_6

00006330 __mspabi_sral_5

00006334 __mspabi_sral_4

00006338 __mspabi_sral_3

0000633c __mspabi_sral_2

00006340 __mspabi_sral_1

00006346 TimerA1Cnfg

00006376 memcpy

000063a0 __TI_zero_init

000063c4 main

000063e8 copy_flash_to_RAM

000063fc _system_pre_init

00006408 C$$EXIT

00006408 abort

00006412 __TI_Handler_Table_Base

00006416 __TI_CINIT_Base

00006416 __TI_Handler_Table_Limit

0000641e __TI_CINIT_Limit

0000fffe _reset_vector

ffffffff __binit__

ffffffff __c_args__

ffffffff binit

UNDEFED __TI_INITARRAY_Base

UNDEFED __TI_INITARRAY_Limit

[727 symbols]