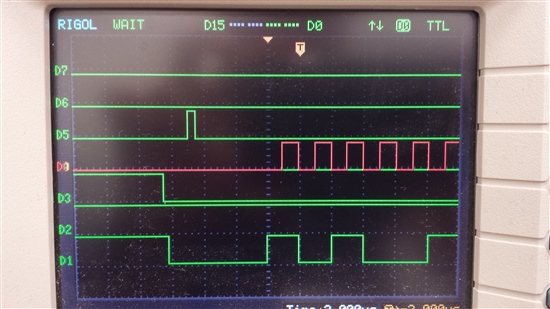

I've posted on a similar topic here and here, but I'm having trouble with my 4-pin SPI Slave module on my MSP430FR5739. The ISR rarely triggers at the times it is supposed to trigger, and when it does, it never correctly transmits the data it is supposed to send, nor does the data collected in the RX buffer match what I see in the oscilloscope.

You may look at my previous posts, but I've posted the main code and the ISR below.

int main(void) {

//WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

SYSTEM_init();

UCA0TXBUF = 0xA5;

STROBE1_HIGH;

//LED1_HIGH;

while (1)

{

while (!(UCA0IV&0x00)) //USCI_A0 Interrupt occuring?

{

STROBE1_LOW;

STROBE2_LOW;

}

UCA0TXBUF = 0xA5;

}

}

#pragma vector=USCI_A0_VECTOR

__interrupt void USCI_A0_ISR(void)

{

switch ( __even_in_range( UCA0IV, 4 ) )

{

case 2:

STROBE1_HIGH;

Temp_SPI_Read = UCA0RXBUF;

printToLEDS(Temp_SPI_Read);

UCA0TXBUF = 0xA5;

break;

case 4:

STROBE2_HIGH;

UCA0TXBUF = 0xA5;

break;

default:

//STROBE1_HIGH;

break;

}

}

I've created some STROBE commands to toggle pins for debugging. I'm not sure what to do, and any suggestions would help. I'll provide more information when it's requested. Thank you