User's Guide of various series of MSP430 all has the Note below in the Section that describes the DINT instruction.

NOTE: Disable interrupt

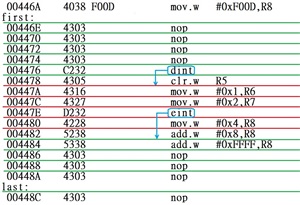

If any code sequence needs to be protected from interruption, DINT should be executed at least one instruction before the beginning of the uninterruptible sequence, or it should be followed by a NOP instruction.

I tried to verify this and my preliminary finding contradicts to this Note. Furthermore, my finding contradicts to a similar Note for EINT.

I wonder if anyone else has ever tried to verify these Notes?