IRQ's should be fast and quick as to not interfere with other IRQ's

Fine-tuned Asm code will help to make them short and sweet.

And I never liked how C handles TAIV registers, a visual mess.

And I don't like to have a offset jump limit, so I use a branch look-up table instead of a jmp table.

NAME TA0_IRQ ; module name

#include "msp430.h" ; #define controlled include file

PUBLIC TIMER0_CCR0 ; make the main label visible outside this module

COMMON INTVEC(1)

ORG TIMER0_A0_VECTOR

DC16 TIMER0_CCR0 ; set irq vector for ccr0

ORG TIMER0_A1_VECTOR

DC16 TIMER0_A1 ; set irq vector for all other

RSEG CODE ; place program in 'CODE' segment

TIMER0_A1

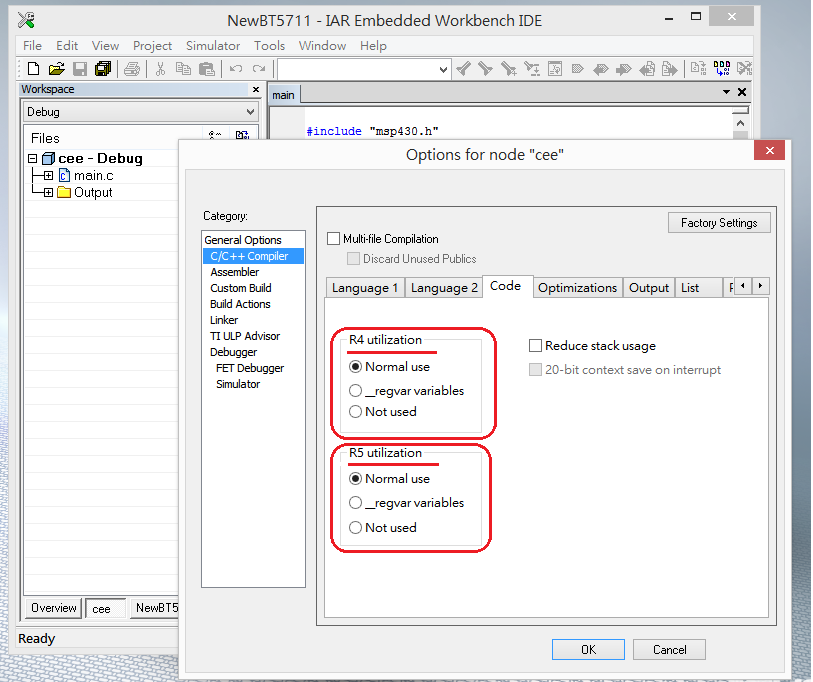

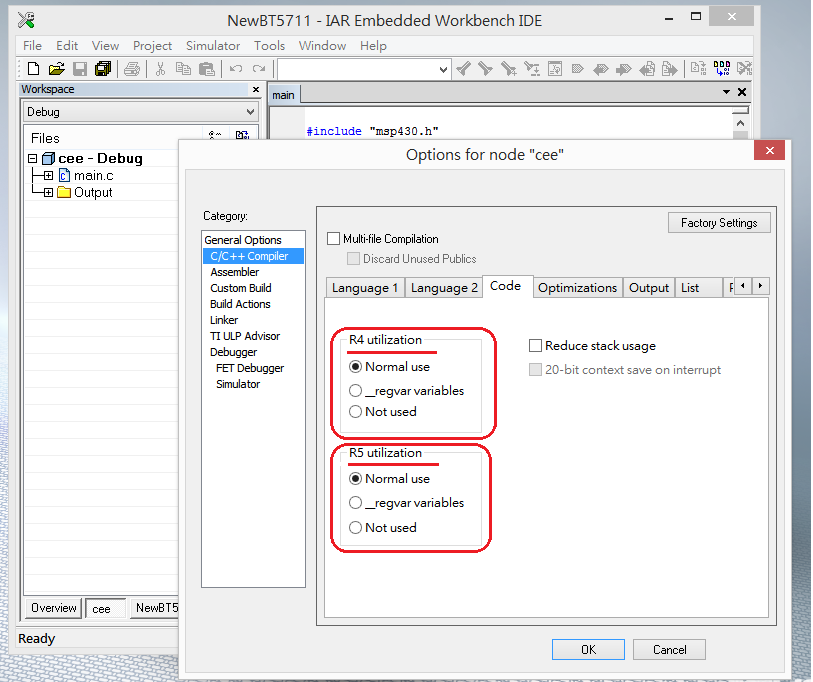

mov.w &TAIV, R4 ; R4 is never used by C, so make it the default IRQ scratch register

mov.w T0_A1_T(R4), PC ; Branch lookup Table, this avoids the ±128 jmp limit

resrvd reti

T0_A1_T DC16 resrvd, TIMER0_CCR1, TIMER0_CCR2, resrvd, resrvd, TIMER0_TA, resrvd, resrvd

TIMER0_CCR0

// CCR0 your code here

reti

TIMER0_CCR1

// CCR1 your code here

reti

TIMER0_CCR2

// CCR2 your code here

reti

TIMER0_TA

// OverFlow your code here

reti

END

Mixing C and Assembler with the MSP430: SLAA140

I attached IRQ templates for PORT 1 & 2 and TA0 and TA1

IAR, Project> Add Files...

add: extern public_name (to the main/calling module)