Hi,

I would like to program MSP430F5259 that is powered from 3.3V and its I/Os are 1.8V.

- Is such scenario being handled gracefully by the FET programmer ? what would be the JTAG lines voltage in this case ? Which rail should I tie VCC_TARGET (if any)

- If using SBW, it is recommended to pull up TEST/SBWTCK line (here, at the end). To which rail ?

- If I need the PCB powered from VCC_TOOL (pin 2 of the JTAG connector) instead of its battery, it will require 3.6V delivered by the programmer.

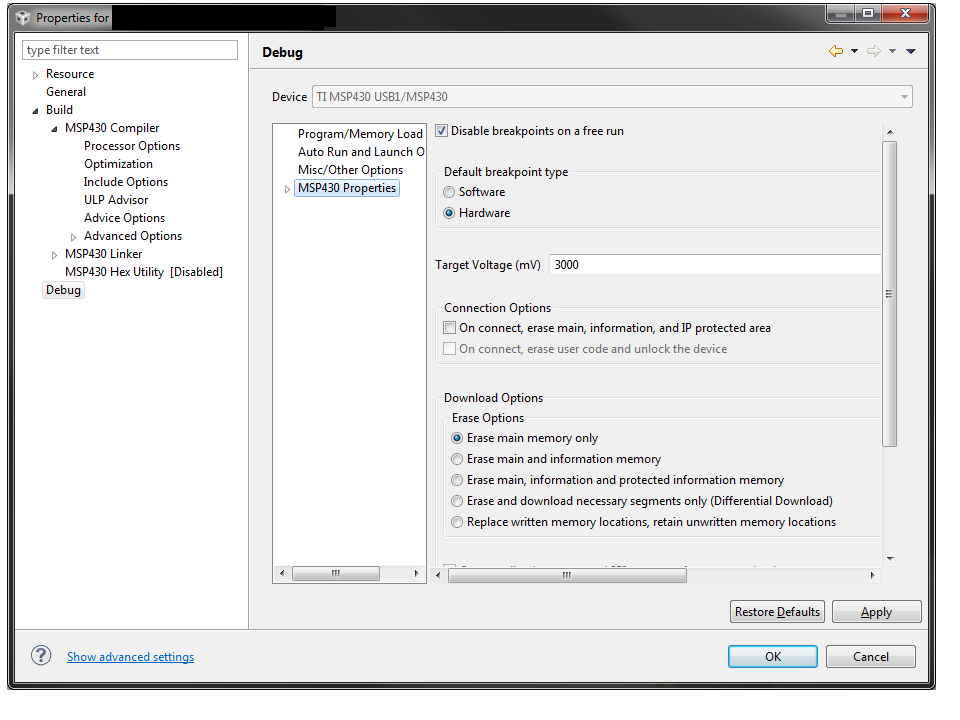

- How can I 'force' the programmer to output 3.6V ?

- In this case to what rail should I tie VCC_TARGET ?

- Will it conflict with the DVIO=1.8V condition ?

Thanks in advance for any support.