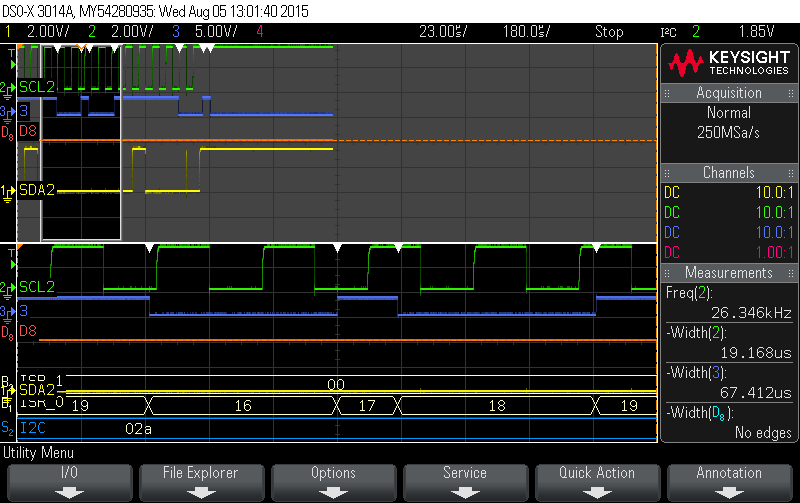

I am using multimaster I2C to connect a couple of MSP430F6779A's. I have gotten the code to send messages back and forth to work just fine. I wrote a search function to send a message to every device on the bus and see which addresses get ACKed. To my surprise the address of the searching MSP as well as the address of the receiving MSP were ACKed.

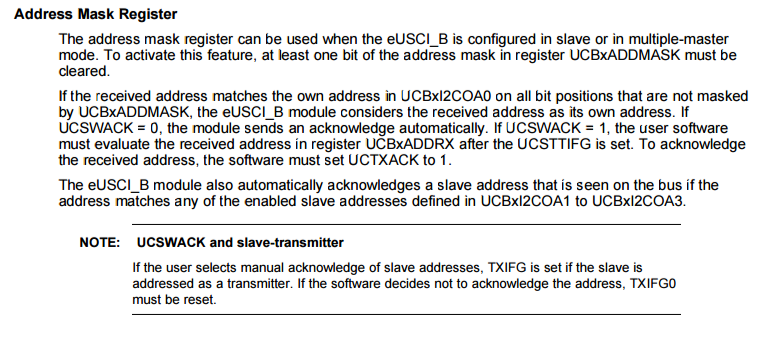

I was expecting that the I2C peripheral would not ACK in slave mode packets that it sends in master mode. This was my experience when writing similar code for the MSP430F2618.

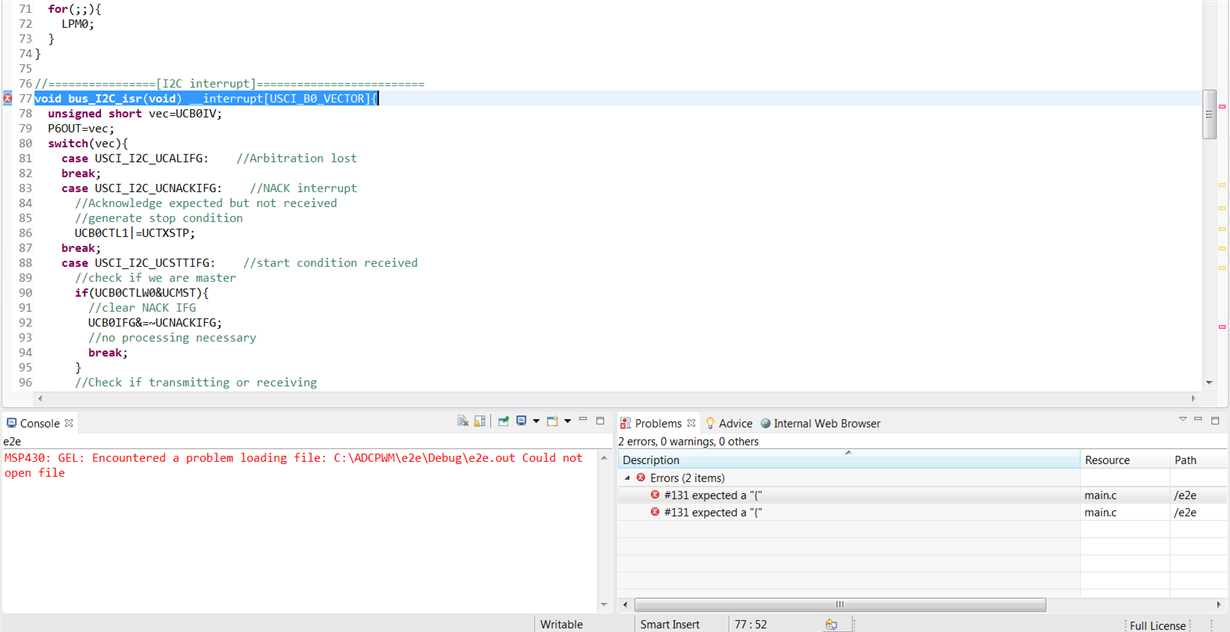

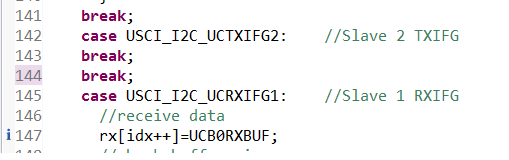

When reading the user guide I saw nothing that said one way or another weather interrupts were expected in response to data transmitted by the I2C peripheral or what is expected in this case. Is it possible to NACK the own address programed into the I2C peripheral? is there a way to detect if the peripheral is sending data to itself or should this be checked in the sending code?