Hi All,

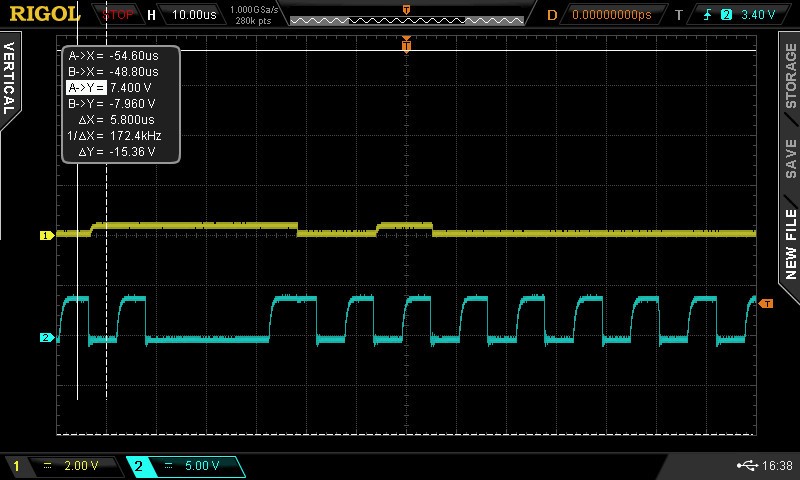

Trying to write a byte to memory and then read it back to confirm the EEPROM communication is working.

Tried using the example code...

#include <msp430f6776.h>

unsigned char TXData;

unsigned char TXByteCtr;

void main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

// Setup P2.5 UCB0SCL, P2.6 UCB0SDA

P2SEL0 |= BIT5 | BIT6; // Set P2.5,P2.6 to UCB0SCL, UCB0SDA

// Setup eUSCI_B0

UCB0CTLW0 |= UCSWRST; // Enable SW reset

UCB0CTLW0 |= UCMST | UCMODE_3 | UCSSEL_2; // I2C Master, use SMCLK

UCB0BRW_L = 12; // fSCL = SMCLK/12 = ~100kHz

UCB0BRW_H = 0;

UCB0I2CSA = 0xA0; // Slave Address is 0A0h

UCB0CTLW0 &= ~UCSWRST; // Clear SW reset, resume operation

UCB0IE |= UCTXIE0; // Enable TX interrupt

TXData = 0x0A; // Holds TX data

while (1)

{

TXByteCtr = 1; // Load TX byte counter

while (UCB0CTLW0 & UCTXSTP) ; // Ensure stop condition got sent

UCB0CTLW0 |= UCTR | UCTXSTT; // I2C TX, start condition

__bis_SR_register(LPM0_bits | GIE); // Enter LPM0 w/ interrupts

__no_operation(); // Remain in LPM0 until all data

// is TX'd

TXData++; // Increment data byte

}

}

//------------------------------------------------------------------------------

// The USCIAB0_ISR is structured such that it can be used to transmit any

// number of bytes by pre-loading TXByteCtr with the byte count.

//------------------------------------------------------------------------------

// USCI_B0 interrupt service routine

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector = USCI_B0_VECTOR

__interrupt void USCI_B0_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_B0_VECTOR))) USCI_B0_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch (__even_in_range(UCB0IV, 30))

{

case USCI_NONE: break; // No interrupts

case USCI_I2C_UCALIFG: break; // ALIFG

case USCI_I2C_UCNACKIFG: break; // NACKIFG

case USCI_I2C_UCSTTIFG: break; // STTIFG

case USCI_I2C_UCSTPIFG: break; // STPIFG

case USCI_I2C_UCRXIFG3: break; // RXIFG3

case USCI_I2C_UCTXIFG3: break; // TXIFG3

case USCI_I2C_UCRXIFG2: break; // RXIFG2

case USCI_I2C_UCTXIFG2: break; // TXIFG2

case USCI_I2C_UCRXIFG1: break; // RXIFG1

case USCI_I2C_UCTXIFG1: break; // TXIFG1

case USCI_I2C_UCRXIFG0: break; // RXIFG0

case USCI_I2C_UCTXIFG0: // TXIFG0

if (TXByteCtr) // Check TX byte counter

{

UCB0TXBUF = TXData; // Load TX buffer

TXByteCtr--; // Decrement TX byte counter

}

else

{

UCB0IFG &= ~UCTXIFG; // Clear USCI_B0 TX int flag

UCB0CTL1 |= UCTXSTP; // I2C stop condition

__bic_SR_register_on_exit(LPM0_bits); // Exit LPM0

}

break;

case USCI_I2C_UCBCNTIFG: break; // CNTIFG

case USCI_I2C_UCCLTOIFG: break; // LTOIFG

case USCI_I2C_UCBIT9IFG: break; // BIT9IFG

default: break;

}

}

The EEPROM is the 24LC02B with slave address 0xA0 I believe.

It just sits in the no_operation() routine and never interrupts.

Any help is appreciated.