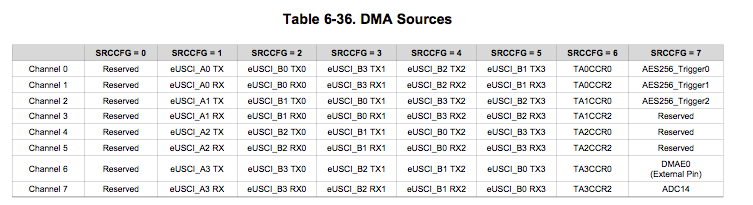

on page 115 of the msp432p401r datasheet, the dma triggers for peripherals is given:

But I haven't found where the behaviour of the eUSCI_Bm_TXn settings is defined.

I've seen some of what Ryan Brown1 has written about this but it doesn't explain what they do. ie. eUSCI_B1 has a TXIFG so if I wanted to run a dma channel that would send data to TXBUF of eUSCI_B1, what channel and configuration would I use?

would I use channel 0 and srccfg 5? channel 2/srccfg 2, etc?