Hello,

I have an MSP430F6779A with an I2C bus activated (to drive a little oled screen).

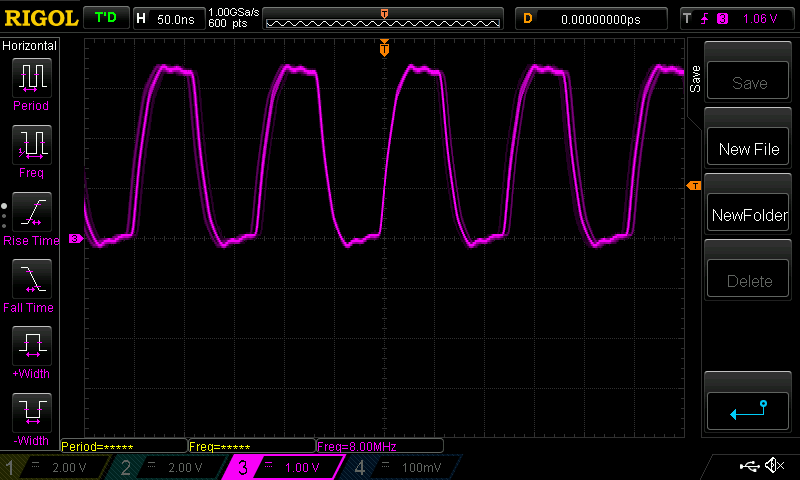

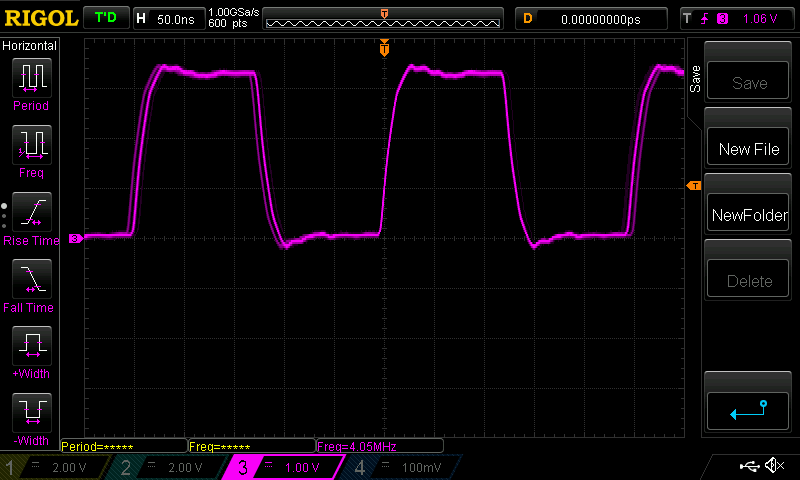

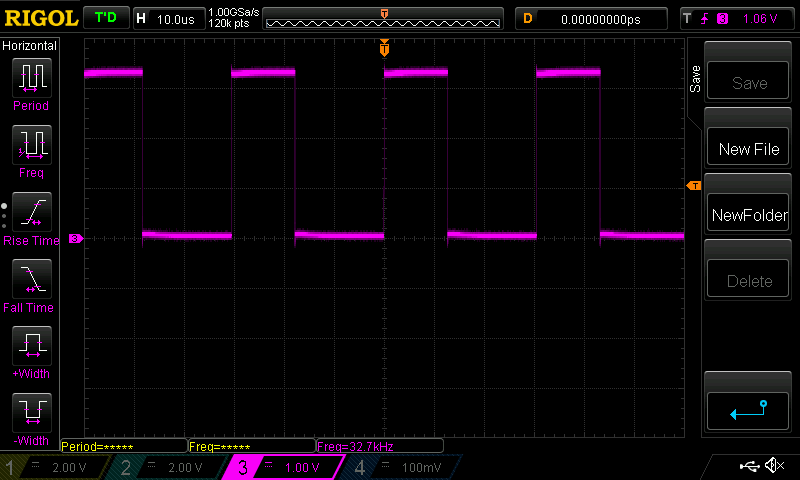

My clocks are : MCLK = 8 MHz, SMCLK = 4 MHz and ACLK (from XT1) = 32,768 kHz.

// Set the correct VCore.

core_setVcoreUp(PMMCOREV_0);

core_setVcoreUp(PMMCOREV_1);

core_setVcoreUp(PMMCOREV_2);

// Configure XT1.

UCSCTL6 &= ~(XT1OFF);

UCSCTL6 |= XCAP_3;

do

{

UCSCTL7 &= ~(XT1LFOFFG);

} while (UCSCTL7 & XT1LFOFFG);

// Configure DCO.

UCSCTL3 |= SELREF__XT1CLK;

__bis_SR_register(SCG0);

UCSCTL0 = 0x0000;

UCSCTL1 = DCORSEL_5;

UCSCTL2 = FLLD_1 | 245;

__bic_SR_register(SCG0);

// Init clocks : MCLK = SMCLK = 8 MHz, ACLK = 32768 Hz.

UCSCTL4 = SELA__XT1CLK | SELS__DCOCLKDIV | SELM__DCOCLKDIV;

// Divide SMCLK by 2 > 4 MHz.

UCSCTL5 |= DIVS__2;

__delay_cycles(250000);

do

{

UCSCTL7 &= ~(XT1LFOFFG | DCOFFG);

SFRIFG1 &= ~OFIFG;

}

UCSCTL6 &= ~(XT1DRIVE_3);

Here what i can see on my oscilloscope. It seems OK...

Now, i configure my I2C bus :

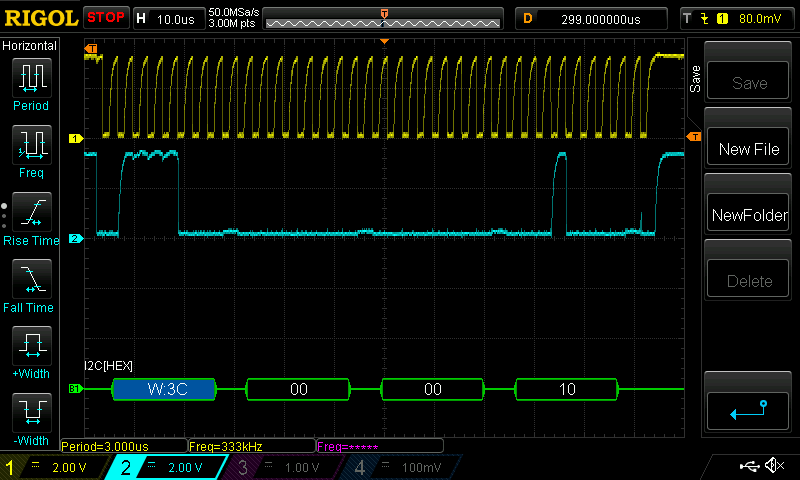

P2SEL0 |= BIT5 | BIT6; // Set P2.5,P2.6 to UCB0SCL, UCB0SDA UCB0CTLW0 |= UCSWRST; // Enable SW reset UCB0CTLW0 |= UCMST | UCMODE_3 | UCSYNC | UCSSEL__SMCLK; // I2C Master, SMCLK UCB0BRW_L = 10; // Divide SMCL by 10 >> 400 kHz UCB0BRW_H = 0; UCB0I2CSA = 0x3C; UCB0CTLW0 &= ~(UCSWRST); UCB0IE |= UCTXIE;

But with this code, my oled screen doesn't work because data are not correct.

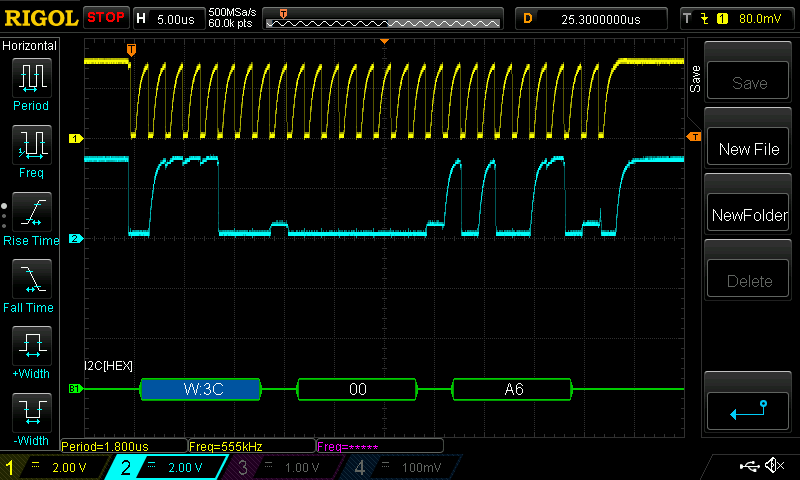

If i check with my oscilloscope, i obtain 333 kHz clock with frequency divider 10, and 4 MHz / 10 is not equal to 333 kHz ???

And if i test with divider 2 (UCB0BRW_L = 2), it works !!! But i obtain a frequency of 555 kHz (while my oled screen has a frequency max of 400 kHz), and the frequency is not equal to 4 MHz / 2 ???

I must be missing something here...

Do you have an idea ?

Thank you :-)

Christophe