I have an MSP430FR6989 launchpad and I am trying to communicate with an OVM camera cube via I2C (Though the camercube is currently disconnected from the circuit, I'm just trying to verify I2C is beginning to communicate). I am monitoring P1.6 and P1.7 at the booster pack pins for the I2C sda and scl, and the output I'm getting on the sda and scl line is very erratic. There is no consistant High to Low "Cycles" on the SCL line, and the SDA does the same. It erratically fluxuated by about 1 volt at times, but it mostly just looks staticy. It appears to me that the eUCB0 may not be controlling the pins. Either way, it doesn't look like it's trying to implement any I2C communication based on the oscilloscope results. I've double and triple checked that my oscilloscope is working properly with other tests I've done. Looking at the code below, is there anything obvious I might be missing? I'm running the DCO at 8MHZ, SMCLK at 1 MHZ, and dividing SMCLK in the UCB0BRW register by 10 to get the desired 100khz frequency for I2C. The code below is just intended to BEGIN I2C communication. I'll implement it when I can verify the eUCB0 module is functioning. If there's any way anyone can help you have no idea how much I would appreciate it!!

I don't see anything in the schematic for any jumpers that I could be missing from what I can tell for those pins on the launchpad...

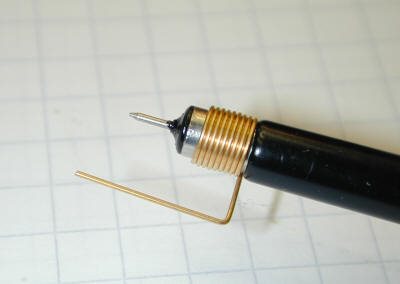

I have a 20k resistor on a breadboard between positive the 3V pin and the SDA, SCL wires.

Code:

void init_i2c();

void singleBytewrite();

void init_pins(){

P2SEL0 &= ~(BIT4 | BIT5);

P2SEL1 &= ~(BIT4 | BIT5);

P4SEL0 &= ~(BIT7);

P4SEL1 &= ~(BIT7);

//Set I2C

P1OUT &= ~(BIT6 | BIT7); //Clear output latch

P1SEL0 |= (BIT6 | BIT7);

P1SEL1 &= ~(BIT6 | BIT7);

//Output MCLK

P4SEL0 |= BIT0;

P4SEL1 |= BIT0;

//Set to output

P2DIR |= BIT4 | BIT5;

P4DIR |= BIT7 | BIT0;

//Set output to high or low

P2OUT &= ~(BIT4 | BIT5);

P4OUT |= BIT7; //Set output to high to reset, and then low when ready

}

void adjustDCO(){

CSCTL0 = CSKEY;

//8MHZ DCO

CSCTL1 |= BIT3 | BIT2;

CSCTL1 &= ~(BIT1);

//Set SMCLK divider to divide by 8

CSCTL3 = (BIT4 | BIT5);

}

void init_i2c() {

UCB0CTLW0 |= UCSWRST; // Enable SW reset (it is naturally, but double check)

UCB0CTLW0 |= UCMST | UCMODE_3 | UCSYNC; //multi-Master, master mode, I2C, synchronous mode, use SMCLK

UCB0BRW = 10; // fSCL = SMCLK/10 = ~100kHz

// The default address is usually 0x42 or 0x6C

UCB0I2CSA = 0x006C; // Where the Master store's the Slaves ID (0x6C for write, 0x6D for read)

// UCB0TBCNT = 2; //I've tried commenting and un-commenting the byte count, but it doesn't seem to make a difference

UCB0CTLW0 &= ~UCSWRST; // set eUSCI_B to Clear SW reset, resume operation

UCB0IE |= UCTXIE0 | UCRXIE0 | UCNACKIE | UCBCNTIE; // Enable Transmit interrupt, receive interrupt, the NACK interrupt, and UCB

}

void singleBytewrite() {

UCB0CTLW0 |= UCTR;

UCB0CTLW0 |= UCTXSTT; // I2C start condition

while ((UCB0IFG & UCTXIFG0) == 0); //Wait until flag set (this is set when the start condition has been generated and data is ready to be written to the buffer)

UCB0TXBUF = 0x006C; // sends slave address (For some reason this also has to be specified in addition to the UCB0I2CSA register

while(UCB0CTLW0 & UCTXSTT); //UCTXSTT flag is cleared as soon as the complete address is sent

UCB0TXBUF = 0x0030;

UCB0TXBUF = 0x002A;

}

int main(void) {

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

PM5CTL0 &= ~LOCKLPM5; // Disables high-impedance mode for FRAM memory

adjustDCO();

init_pins();

while(1){

init_i2c(); // starts I2C function with OV5647 slave

singleBytewrite(); // starts function to write 1 byte to slave register

}

}