Hello Sir,

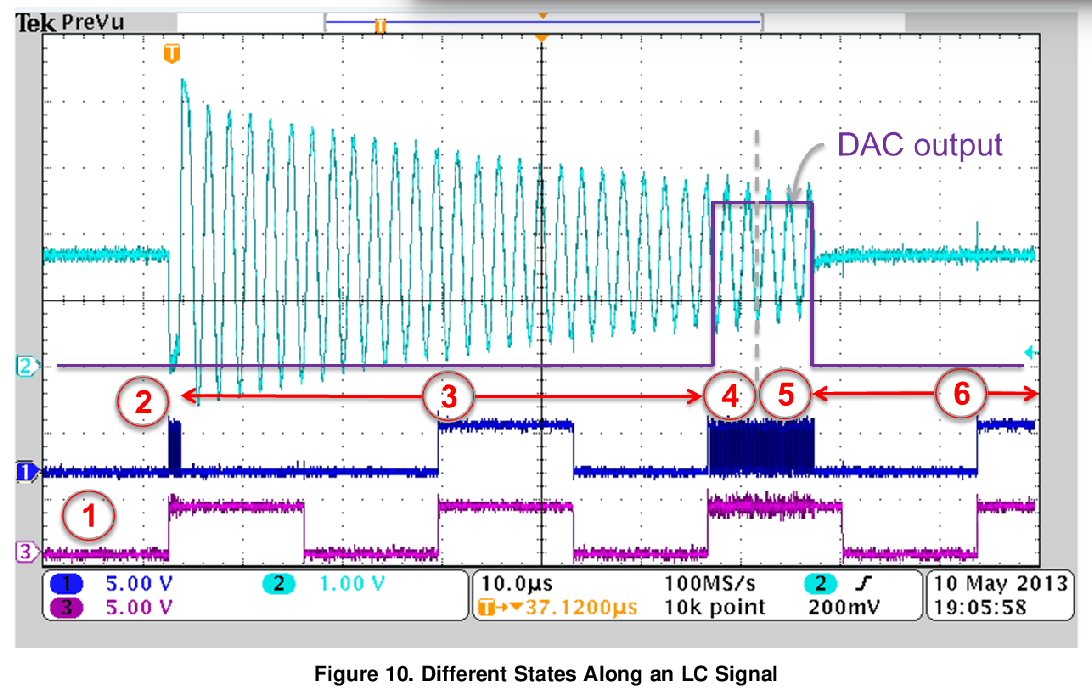

For waves mentioned in "slaa639_LC Sensor Rotation Detection With MSP430™ Extended Scan" as below:

We think, channel 3 should be ACLK and channel 2 measures the LC sensor signal. But seems no clearly description about what signal on Channel1.

Would you please help tell what signal shown on channel 1? Via any pin we can obsearve this signal with scope?

Best regards

Jacky