I have a question regarding one of the issues discussed in the errata data sheet for the MSP430FT6989:

USCI41 eUSCI Module Function UCBUSY bit of eUSCIA module stuck to 1 when device is in SPI mode. Description When eUSCIA is configured in SPI mode, and the last transfer bit changes from 0 to 1, the UCBUSY bit gets stuck to 1. This happens in all four combinations of Clock Phase and Clock Polarity options (UCAxCTLW0.UCCKPH & UCAxCTLW0.UCCKPL bits). There is no data loss or corruption. Because the USCBUSY bit is stuck to 1, the clock request stays enabled and adds additional current consumption in low power mode operation. Workaround Check on transmit or receive interrupt flag UCTXIFG/UCRXIFG instead of UCBUSY to know if the UCAxTXBUF buffer is empty or ready for the next complete character.

I've definitely identified that this is an issue - or perhaps have verified it - but if I'm using UCA0 as a SPI Slave; and I'm wanting to transfer a SPI packet when receiving; I'm a little unclear on the best method to determine if the port is still busy; especially when checking that the SPI packet has been transmitted.

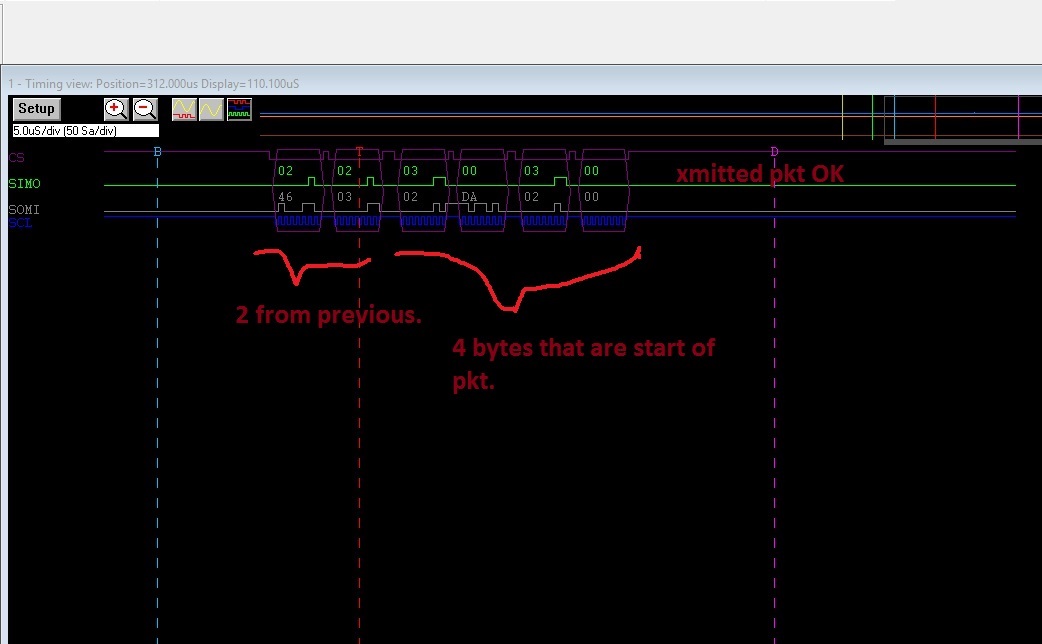

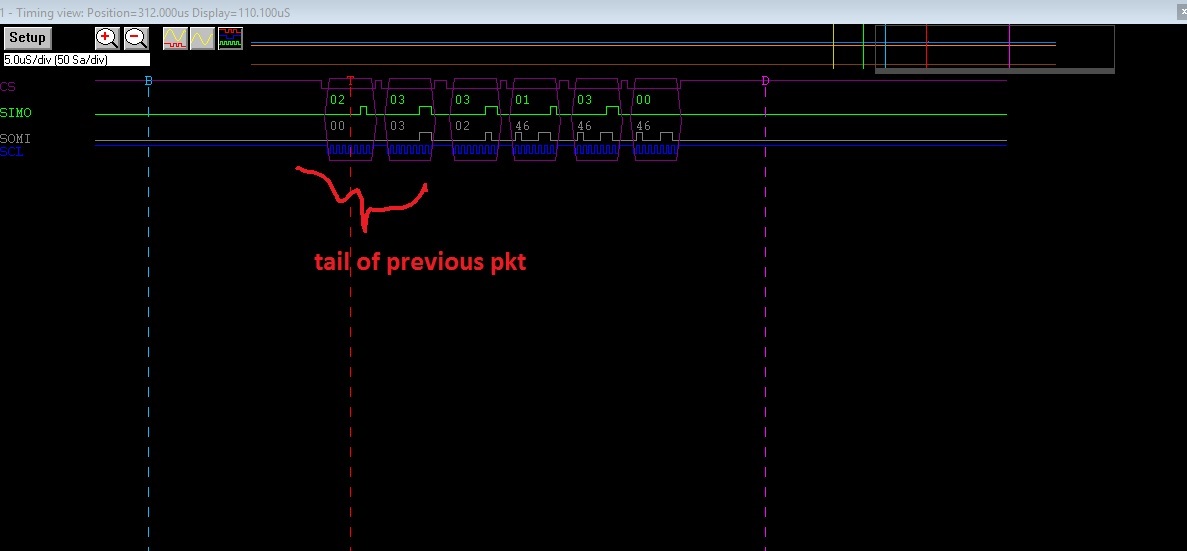

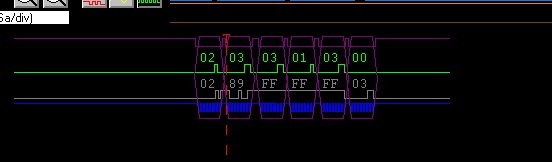

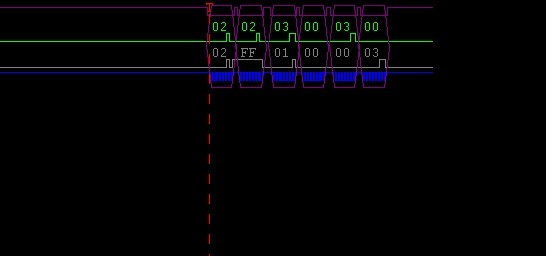

Right now I'm seeing the packet being sent by as being misaligned from what I can tell by 2 bytes; meaning the first two bytes are from the previous data packet.

I suppose USCI45 isn't an issue in SPI Slave Mode, correct?

USCI45 eUSCI Module Function Unexpected SPI clock stretching possible Description In rare cases, during SPI communication, the clock high phase of the first data bit may be stretched significantly. The SPI operation completes as expected with no data loss. This issue only occurs when the USCI SPI module clock (UCxCLK) is asynchronous to the system clock (MCLK). Workaround Ensure that the USCI SPI module clock (UCxCLK) and the CPU clock (MCLK) are synchronous to each other.

This is fairly straight forward; but I was wondering about the best way to determine when the transmission was still taking place since this is a slave - something like this won't work due to the errata:

while ( EUSCI_A_SPI_isBusy(EUSCI_A0_BASE)== EUSCI_A_SPI_BUSY ) //SPI still sending data? - errata

;

I'm also doing this with DMA - 2 channels - 1 for receive and one for transmit.

For this errata:

DMA7 DMA Module Function DMA request may cause the loss of interrupts Description If a DMA request starts executing during the time when a module register containing an interrupt flags is accessed with a read-modify-write instruction, a newly arriving interrupt from the same module can get lost. An interrupt flag set prior to DMA execution would not be affected and remain set. Workaround 1. Use a read of Interrupt Vector registers to clear interrupt flags and do not use readmodify-write instruction. OR 2. Disable all DMA channels during read-modify-write instruction of specific module registers containing interrupts flags while these interrupts are activated.

Is it OK to execute this:

DMA_disableTransferDuringReadModifyWrite();

DMACTL0 |= DMARMWDIS; // and/or?

DMACTL1 |= DMARMWDIS; // and/or ?

Thanks,

John W.