Other Parts Discussed in Thread: MSP-EXP430FR2433, MSPDRIVERLIB, MSP430FR2433, MSP430WARE

I have been writing a SMBus slave for Read Word, Write Word, and Block Read protocol with and without PEC, using the MSP430F5329.

I have been using the Python SMBUS libraries on the Raspberry Pi to test the code. I have gotten the Read word with PEC and Without PEC.

I can not get the Read Block to work, and I know the bytes I am sending are right. Documentation is nonexistant. So I am looking for something else.

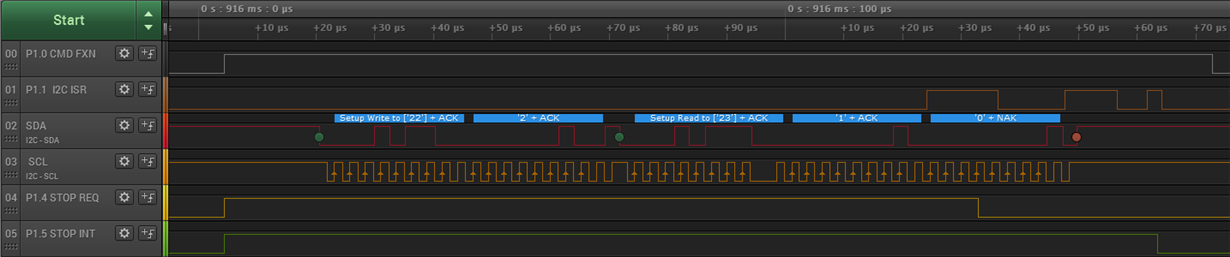

In the process of looking at the SMBus protocol more closely in both the read word and block read, the last data byte sent by the slave is NAKed by the master, then the master sends a Stop. I had not noticed it before.

My code lets me know every time an I2C interrupt is generated and logs the type of interrupt. I have never seen a NAK interrupt come through. So now I am very suspicious of the Raspberry Pi code.

I figured I might as well use another MSP430 chip as my I2C Master and picked up the MSP-EXP430FR2433. I was looking at the library functions in the MSPDRIVERLIB: DriverLib for MSP430 devices and can not figure out a way to send a NAK after a the last byte is received, as the SMBus specification requires.

For example Figure 31 in System Management Bus (SMBus) Specification Version 3.0

<Master Start> <Master Address> <Master Wr> <Slave ACK> <Master Command Code> <Slave ACK> <Master Restart> <Master Address> <Master R> <Slave ACK>

<Slave Data byte Low> <Master Ack> <Slave Data byte High> <Master NAK> <Master Stop>

What am I missing?

How do I send the Master NAK in response to the Slave sending the Data byte High? It seems to be ACKed automatically.

Kip