Other Parts Discussed in Thread: MSP-FET

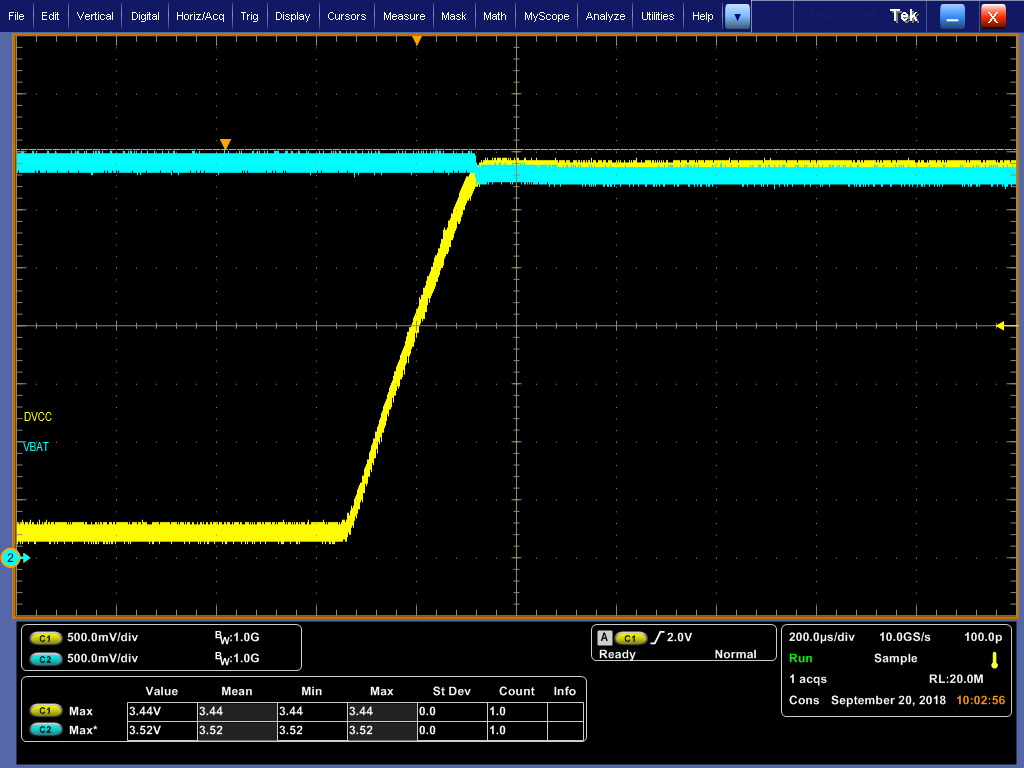

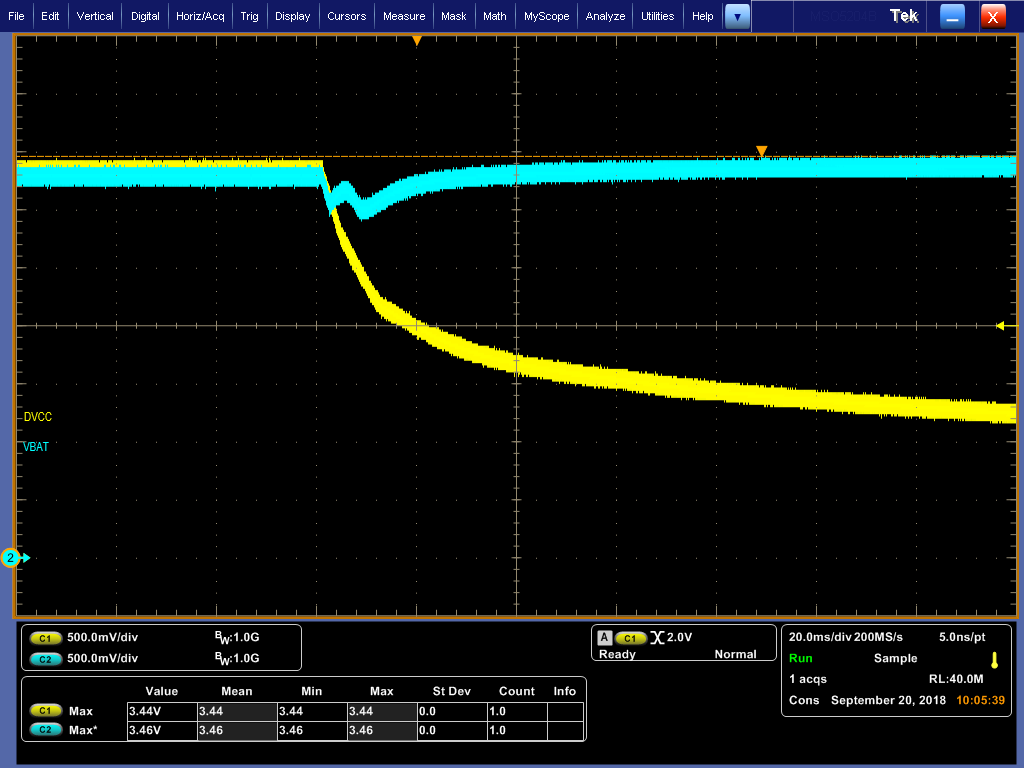

I am having an RTC_B problem with board which incorporates an MSP430F5335. We have shipped around 800 of these boards with very little problems seen. On rare occasions though, during production, we are seeing an issue where the RTC either doesn't increment (see the following thread started by me: https://e2e.ti.com/support/microcontrollers/msp430/f/166/t/527645) or the RTC appears to increment by several years each second (see the following related link: https://e2e.ti.com/support/microcontrollers/msp430/f/166/t/675454?tisearch=e2e-sitesearch&keymatch=RTC_B). It seems that the only way to correct the issue is to remove both DVCC and VBAT. Removing DVCC only does not resolve the issue. We have closely followed the recommended procedures described in the "Using the MSP430 RTC_B Module With Battery Backup Supply" application report SLAA665B. In the past week, we have had 2 boards where the RTC doesn't increment and 2 where it incremented very quickly. The second link above was handled offline so I could not follow it to the solution. Is there anyway that someone could contact me to discuss the solution. Offline will be fine if necessary.

Thanks,

Greg