Other Parts Discussed in Thread: MSP430FR5994, , ENERGYTRACE

I just tripped over Erratum ADC65 in the MSP430FR5994 Errata Sheet (SLAZ681M). This is the one where the ADC12 keeps running its clock between conversions.

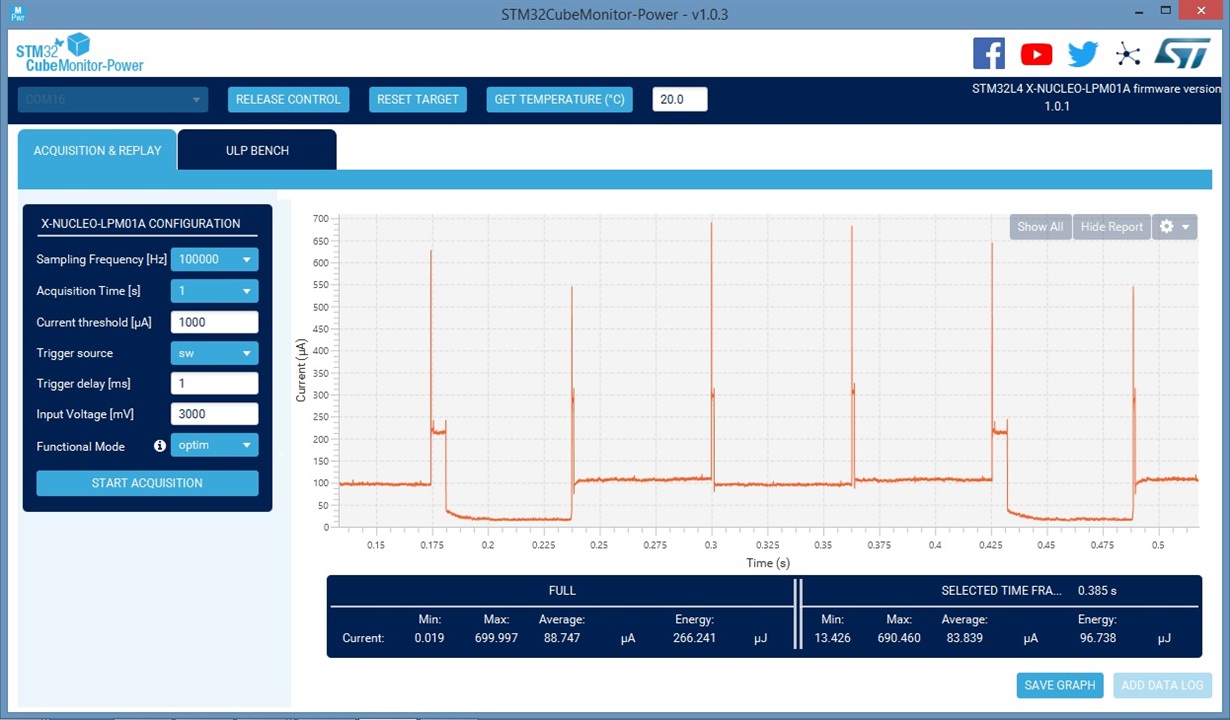

I'm pretty sure I observed the same phenomenon in the MSP430FR2311 ADC some months back, but I don't see it described in the Errata Sheet (SLAZ679P). It was on a Rev A (not "X") device, and amounts to about 80uA (extra). I wouldn't be surprised if it happens on other FR2 devices, but all I have is "X" versions of those.

Should I report this to someone? I have a test program and some screen captures, but maybe the people who investigated ADC65 have something better.

This anomaly is perhaps more significant for the FR2 devices since they don't have DMA.