Other Parts Discussed in Thread: MSP430WARE, MSP430F5438A,

Hi,

I would like to take the discussion further where I left last time. Please look at my previous post which was almost 9 months back.

https://e2e.ti.com/support/microcontrollers/msp430/f/166/t/766491

Now, I am using FPGA between my Communication Transceiver and MSP430.

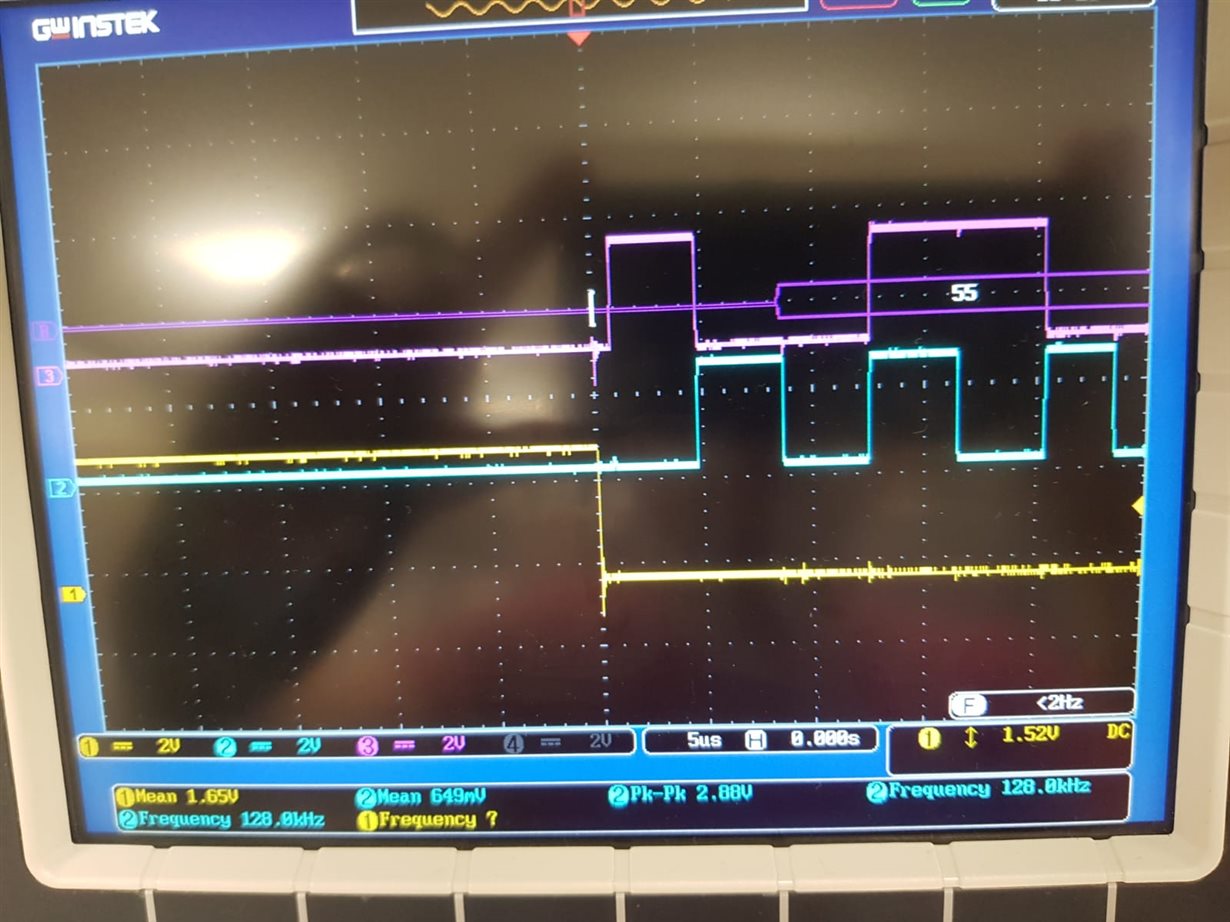

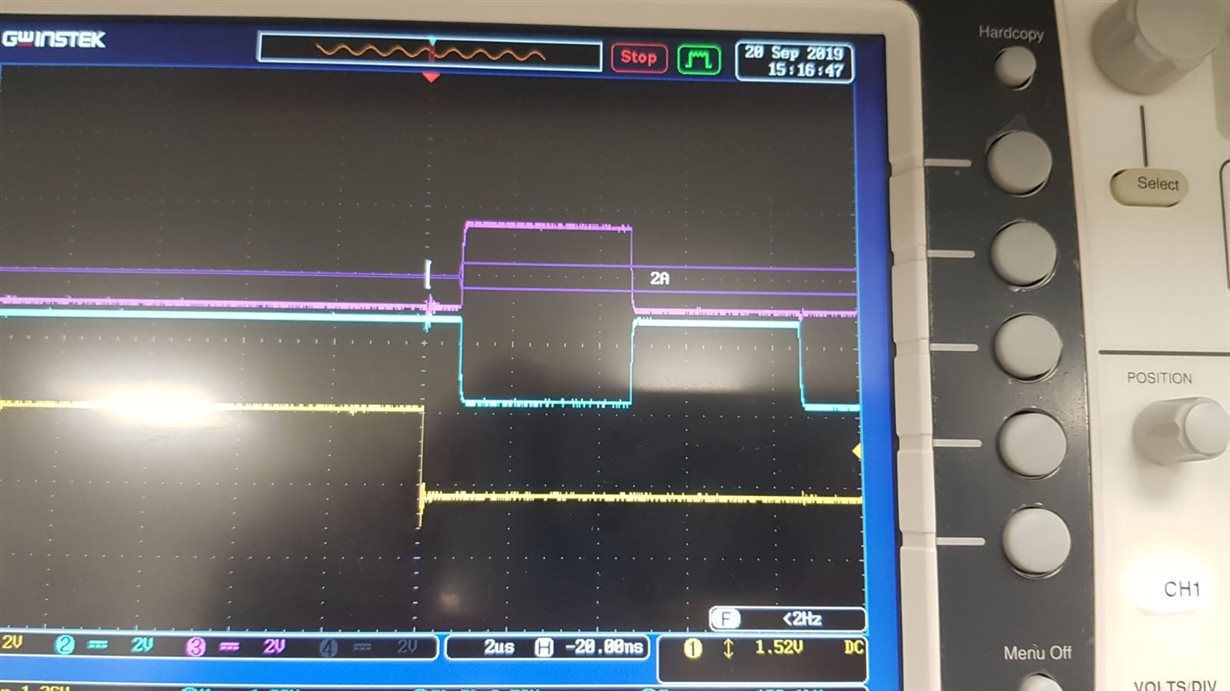

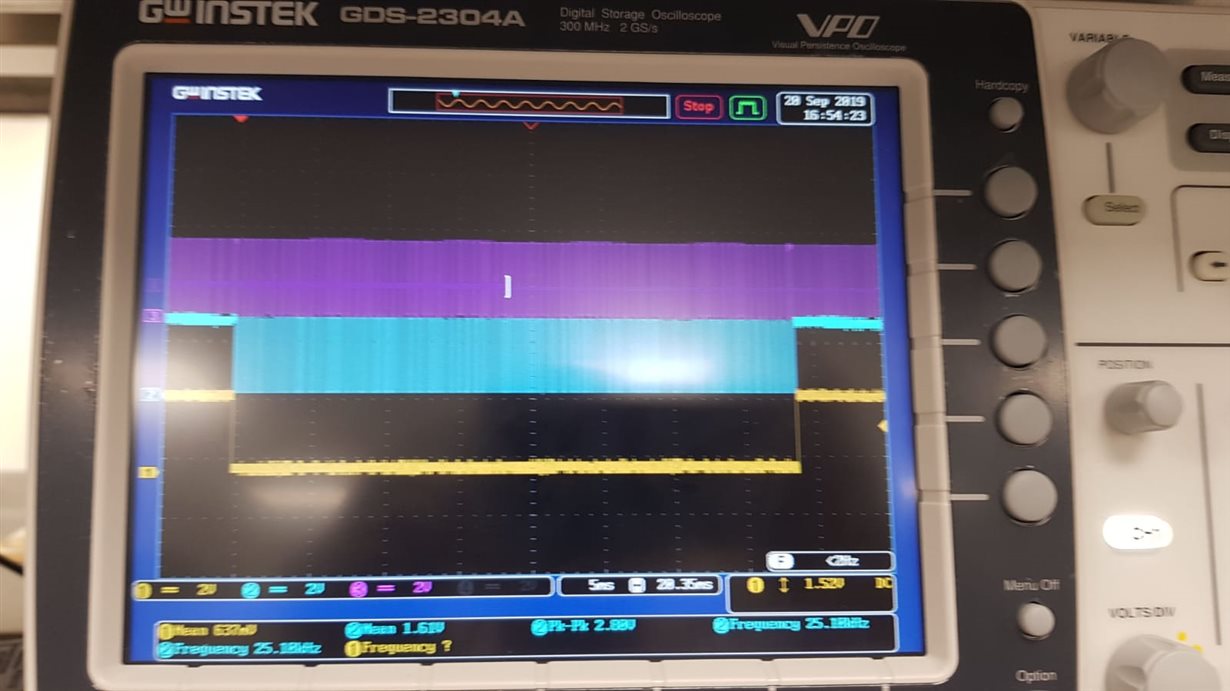

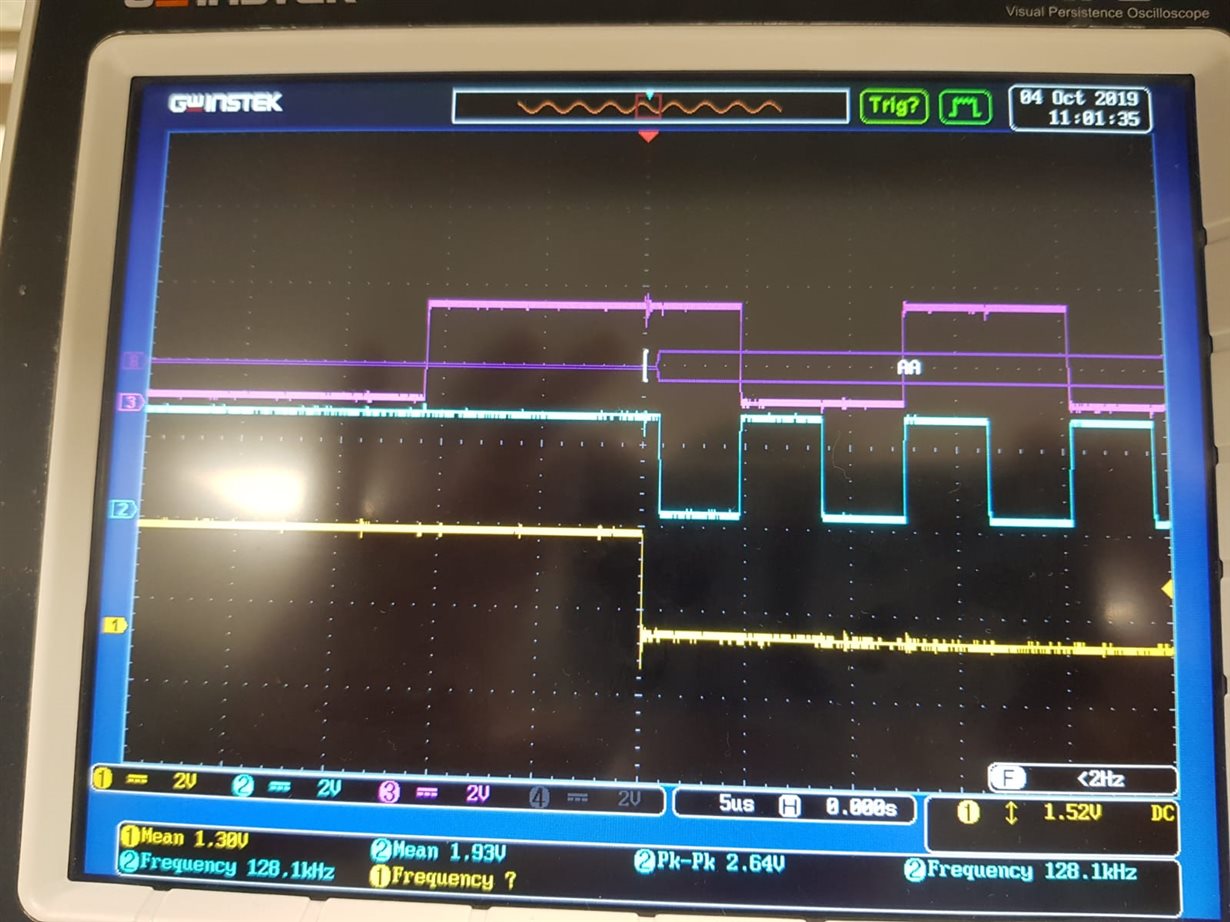

FPGA will constantly receive DATA and CLK from the Communication Transceiver and look for a pattern of DATA sampled at the CLK provided by the communication transceiver. This pattern of data we call as start of frame (SOF). Once it receives SOF, it will set one of its pin as chip select (CS active high) to high and forward the CLK, DATA and CS to MSP430 SPI slave. We have a pattern of data for end of frame as well (EOF). And once FPGA sees the EOF, it will deselect the MSP430 SPI slave by setting the CS as low.

When I tried to run my system and receive, my MSP430 sometimes receives the DATA properly and sometimes DATA shifted by few bits (around 1-4 bits).

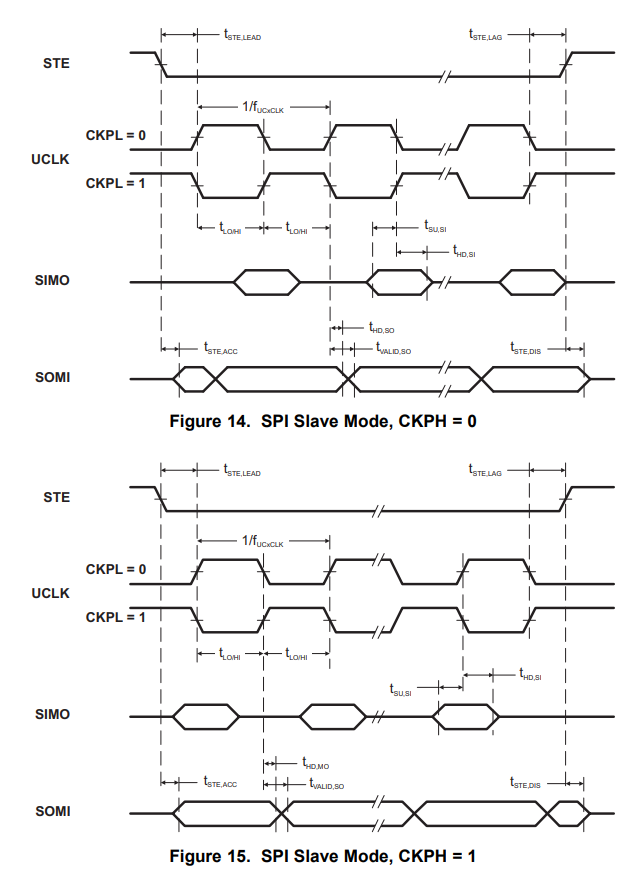

I realised that my CS was getting activated at the same edge of the CLK where DATA is to be sampled.

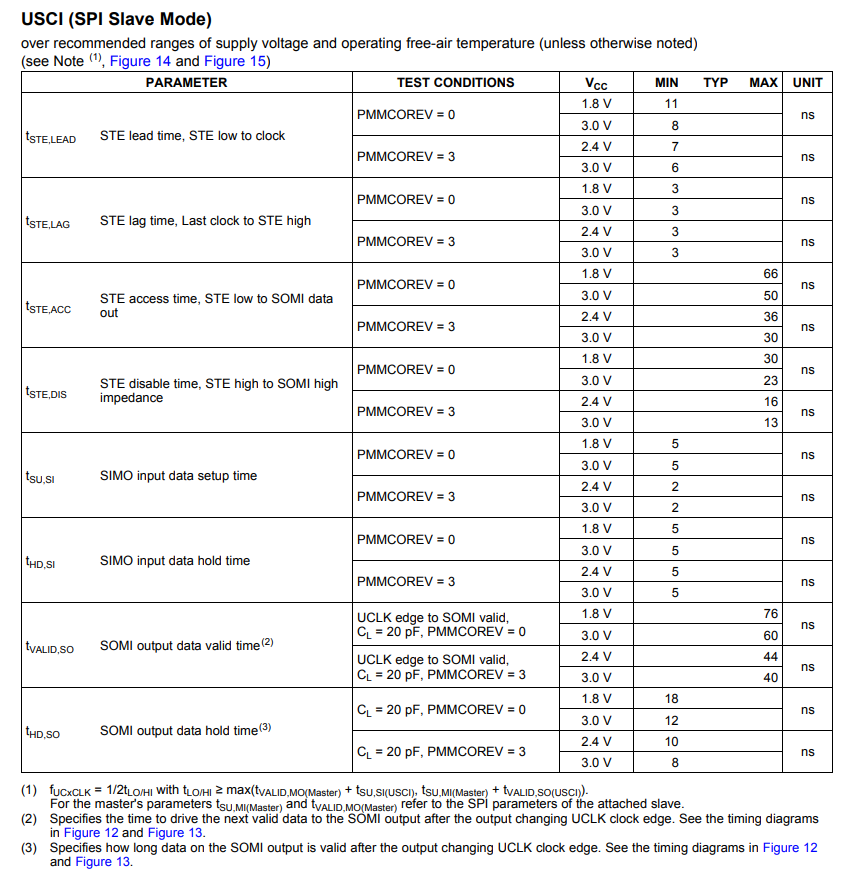

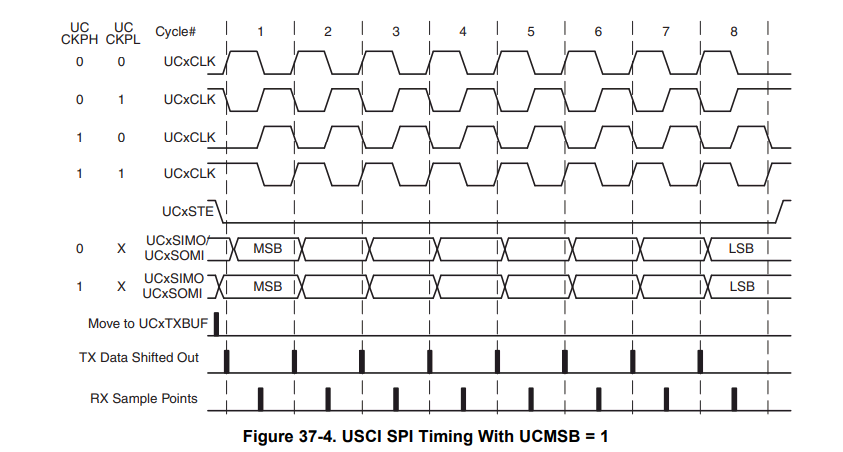

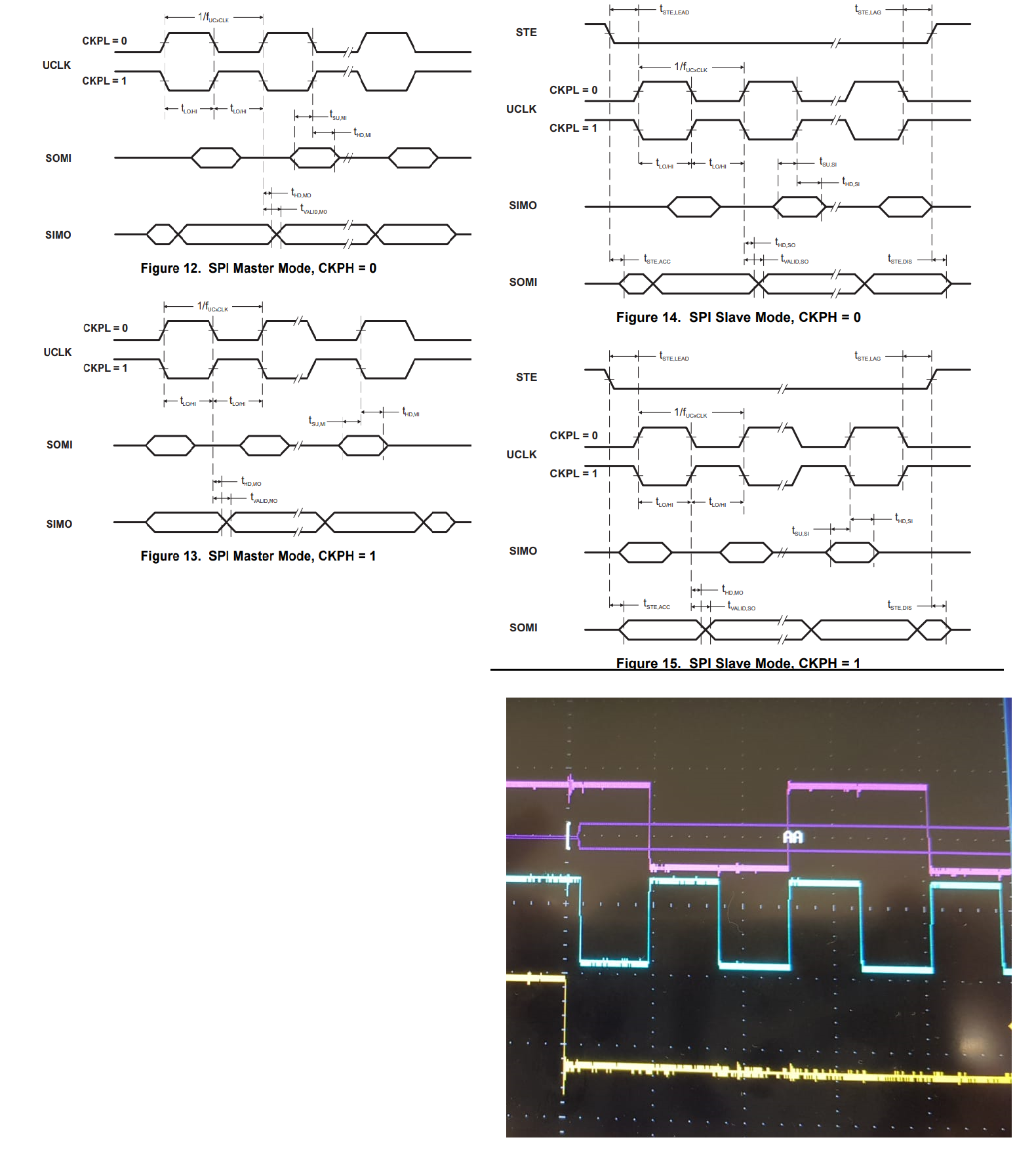

Now it seems like I am kind of creating my own SPI master using FPGA. That means I need to handle the timing constraints as mentioned below:

So my CS should come at least 11 ns earlier. I plan to put CS high around CLK/4 time earlier than the next CLK and DATA. Would that be OK?

Can anything else also cause the bit shift issue? Also do let me know if I have to handle something else as well.

I would like to know how SPI slave triggers an interrupt for receive. Does it trigger based on 8 input SPI CLK after the SPI is enabled?

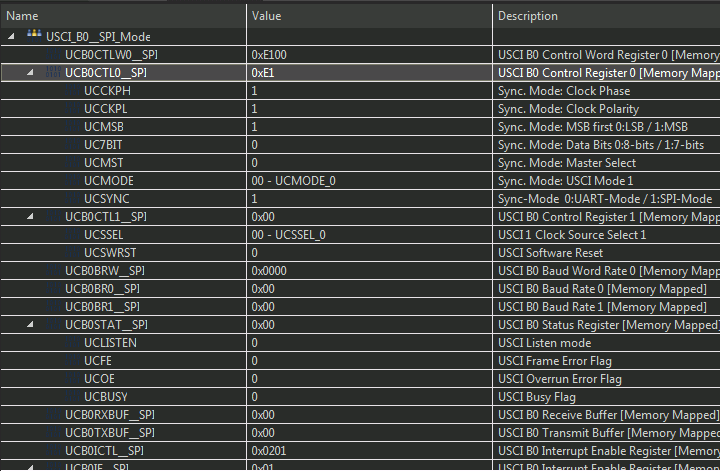

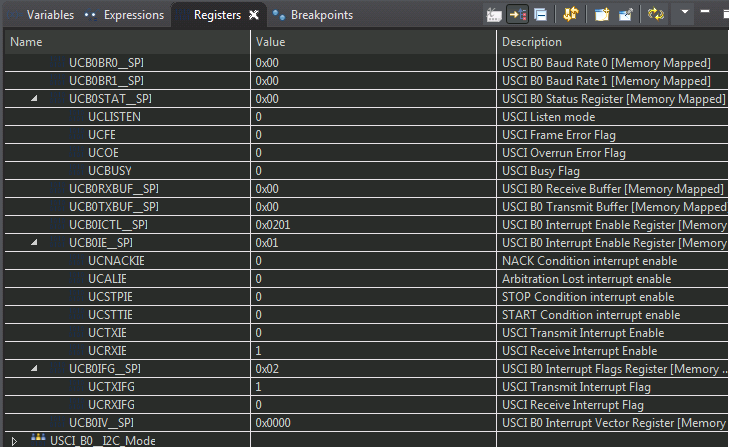

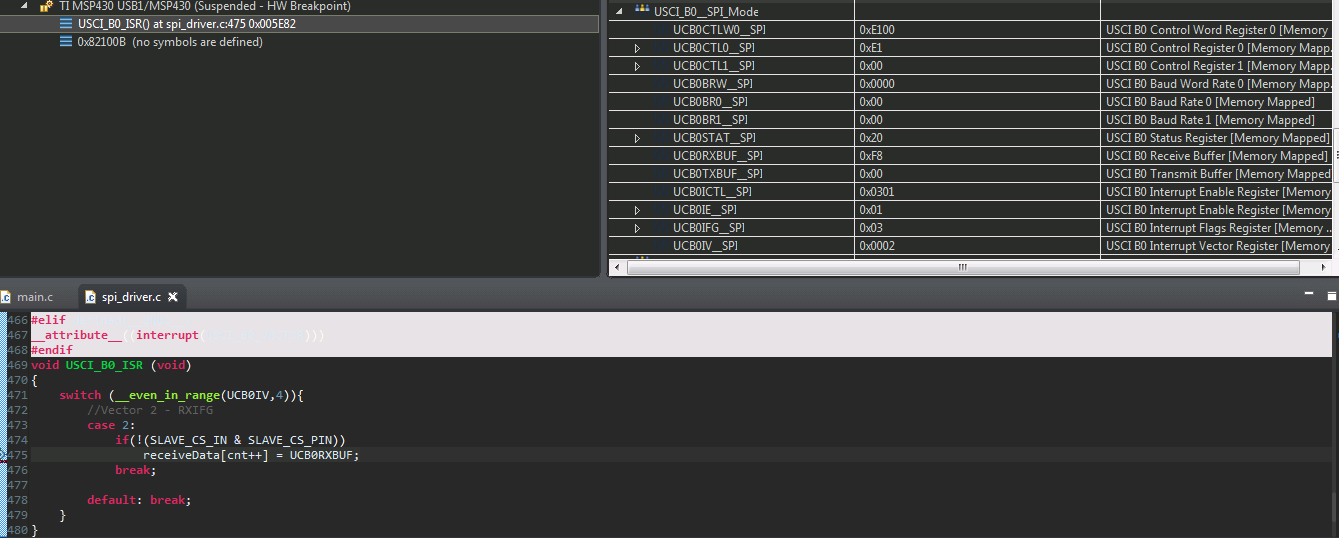

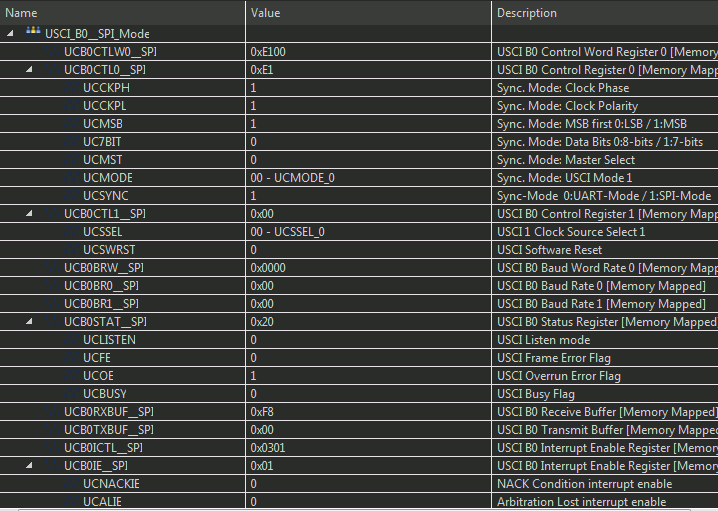

My ISR looks like below (used reference from SPI slave MSP430F5438A example from MSP430ware) :

#define SLAVE_CS_IN P3IN

#define SLAVE_CS_DIR P3DIR

#define SLAVE_CS_PIN BIT0

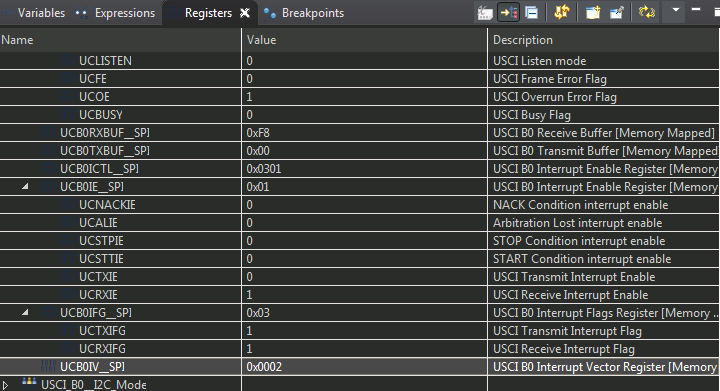

void USCI_B0_ISR (void)

{

switch (__even_in_range(UCB0IV,4)){

//Vector 2 - RXIFG

case 2:

if(SLAVE_CS_IN & SLAVE_CS_PIN)

receiveData[cnt++] = UCB0RXBUF;

break;

default: break;

}

}

Thanks and Regards,

Ankit