Hi Forum,

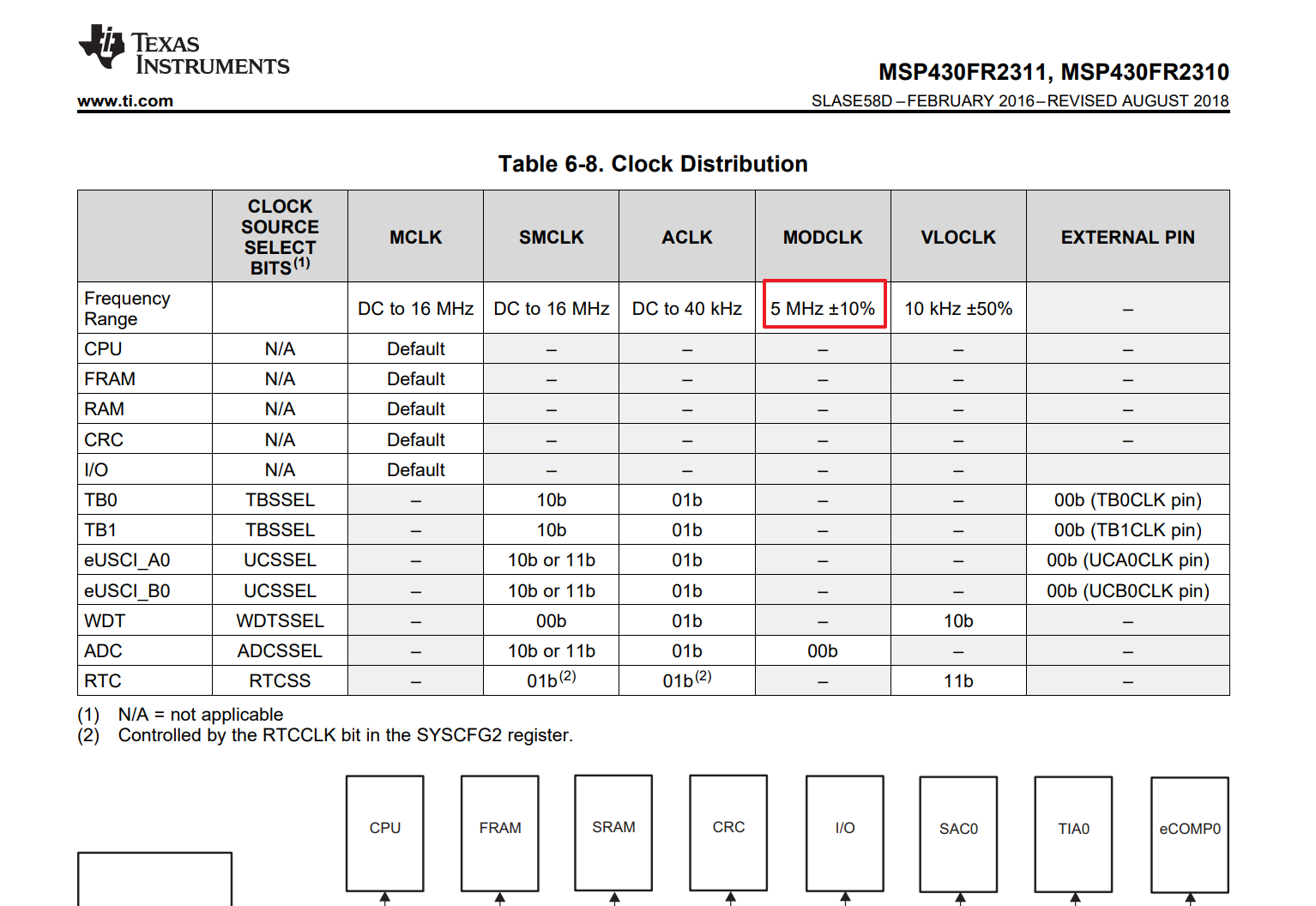

Maybe I am reading the specs wrong. The following table, while referencing 16MHz, seems to indicate a lock frequency much closer to the target than I am getting. Two launchpads are being used, this one using REFO, and the other using XT1, and both exhibit the same results. Both MCLK freqs are down 10% to 12%. The spec sheet shows.....

%1.0%FLL lock frequency,16 MHz,–40°C to 85°C–2.0%2.0%, while the XT1 spec shows +- 0.5%.

***********************************************

THIS IS AN EDIT TO THIS POST: Just want to add a couple of details Both ACLK and SMCLK were mapped to the header pins on both launch pads. Both REFO and XT1 are spot-on when checked with an oscope. SMCLK (and hence MDCLK) are 10 to 12% long in period. When REFO and XT1 are used as a timer base, and LED's are used to blink at exactly 1sec, both pass the "clock-on-the-wall" click test, an aveage over 10 seconds. SMCLK fails the "clock-on-the-wall" click test (I can hear the clock tick as it goes around). Not exactly scientific, but it works.

THIS IS THE SECOND EDIT TO THIS POST: Bits 9,8 of CSCTL7 were polled and resulted in 10, DCOCLK IS CURRENTLY TOO FAST, which indicates FLL UNLOCK. Both bits would have to have returned 0 to show that the FLL was locked. This result is in agreement with the oscope trace? And to make matters more confusing, CSCTL7 bit 4, FLLULIFG reads 0, bit 0 DCOFFG reads 0, and bit 12 FLLULPUC reads 0.

THIS IS THE THIRD EDIT TO THIS POST. Something I noticed on previous days, but was too busy to do anything about. The REFO board, MSP430FR2311 appears to do a PUC reset about every 5 minutes. Otherwise the board, and the downloaded program, function as they should.

**********************************************.

I hope not to bury anyone with excessive look ups, but here are the CS registers....

void Init_Clock()

{

CSCTL1= 0b0000000000000110; /* factory trim, 8MHz, NO modulation */

CSCTL2= 0b0001000000000001; /* fDCOCLK=/2 (FLLD=001), FLLN=1 */

CSCTL3= 0b0000000000010000; /* REFO high power,FLL ref is REFO,FLL divider= 1 */

CSCTL4= 0b0000000100000000; /* ACLK source is REFO,MCLK and SMCLK source is DCOCLKDIV */

CSCTL5= 0b0001000000000000; /* VLO off,SMCLK on,MCLK divider=1 */

CSCTL6= 0b0000000010000000; /* ACLK divider= 1,high power, low freq,bypass,1-4MHz,AGC,always on */

If the MODCLK accuracy is simply this far off, then just please let me know.

Thanks in advance,

Robert.