Other Parts Discussed in Thread: REF2033

Hello,

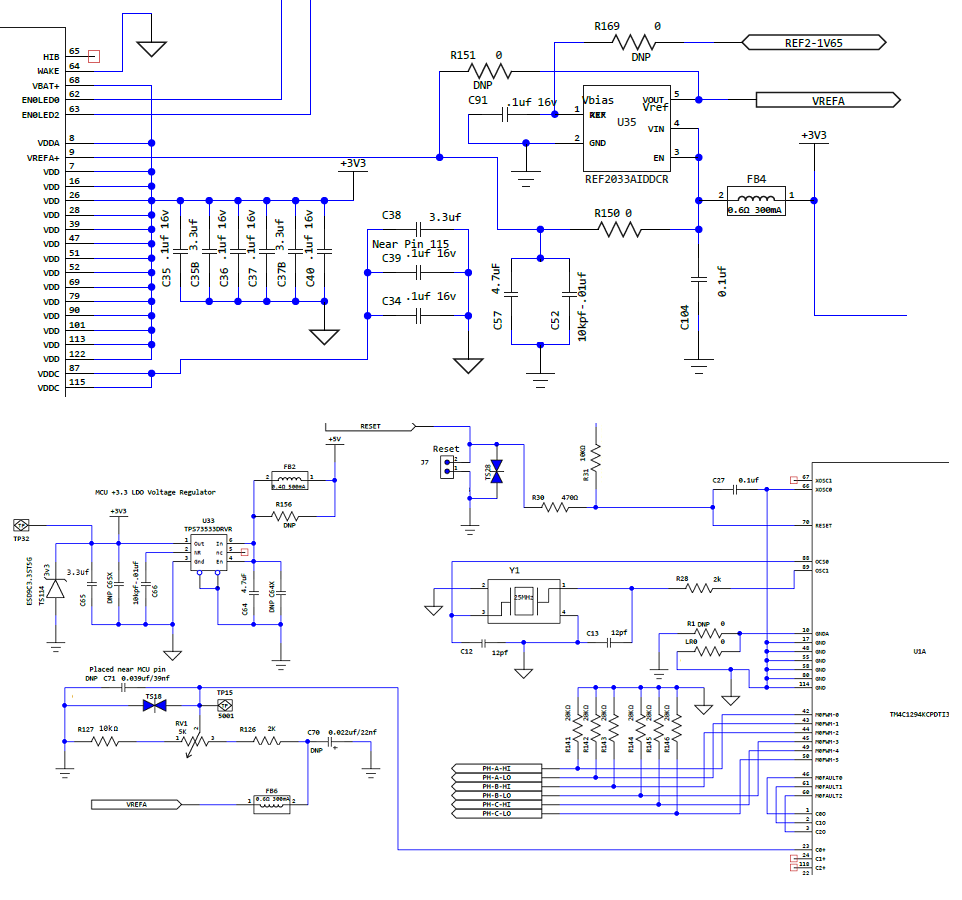

Yet another MCU has early perished powering analog comparator C0+ (PC6) external via REF2033. Note C0+ threshold via RV1 set 2.54v (<3v3) yet VDDA pins 8 to 10 GNDA was (12 ohms), MCU out of circuit. Simply touching DMM probe on TP15 to check C0+ threshold after detecting several unwarranted C0+ faults somehow caused MCU failure. Note wearing static wrist band and PCB outer perimeter foil trace being connect to earth ground, doubtful static was cause.

Besides several TVS diodes did not stop either MCU failure. ADC0/1 are both configured internal VREFA+. Direct powering FB6 from +3v3 does not causes MCU early failure but does allow transients to enter C0+ input, RE2033 seems to provides transient isolation. REF2033 is powered from the same +3v3 LDO as VDD. LR0 being 0R chip or even hard solder bubble to DGND made no difference in post mortem failure analysis.

What is it about configuration also causes VDD to short DGND (<1.3 ohms), MCU out of circuit? Does configuring analog comparators CnO (OR'd outputs OD) have some issue with C0+ external power source? That other configuration VR1 (C0+) powered direct +3v3 worked for several months without failure. Can we damage claim these MCU failures?