Hello,

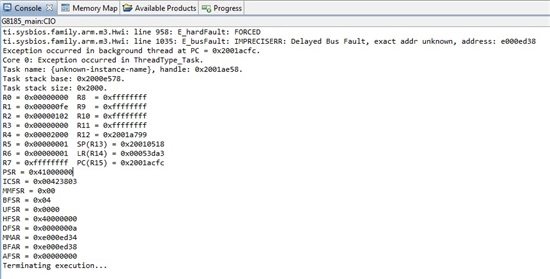

I am trying to run my section of main code starting at address 0x4c000 when I get a forced hard fault because of a delayed bus fault or an undefined instruction. It always happens at LR(R14) = 0x00053da3, which is during the execution of the first task my bios runs. I am not sure if it is normal for an address to line up like that.

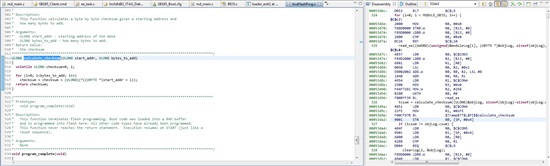

My stack and heap size seem to be reasonable but maybe stack is still too small? I don't know why things would go awry at this point every time. Here is a screen shot of the disassembly at the last address.

I am not sure what to check from here or what other potential problems could cause this. I am also wondering if it could be a problem with my mapping though the command file.

ARM Compiler 5.1.7, TI-RTOS 1.21.0.09, XDCtools 3.25.4.88

Thanks for any help/advice